# 近接ワイヤレス接続が創る 3次元集積計算システム

慶應義塾大学理工学部電子工学科 黒田忠広 www.kuroda.elec.keio.ac.jp

#### 内容

- 1. 磁界結合によるチップ間通信 ThruChip Interface (TCI)

- 2. TCIの応用

- 3. 電磁界結合によるボード間通信 Coupled Transmission Line (CTL)

チップレベル 3D IC μm, 5Tbps, TCI

ボードレベル 非接触コネクタ mm, 50Gbps, CTL

#### 内容

- 1. 磁界結合によるチップ間通信 ThruChip Interface (TCI)

- 2. TCIの応用

- 3. 電磁界結合によるボード間通信 Coupled Transmission Line (CTL)

チップレベル 3D IC μm, 5Tbps, TCI

ボードレベル 非接触コネクタ mm, 50Gbps, CTL

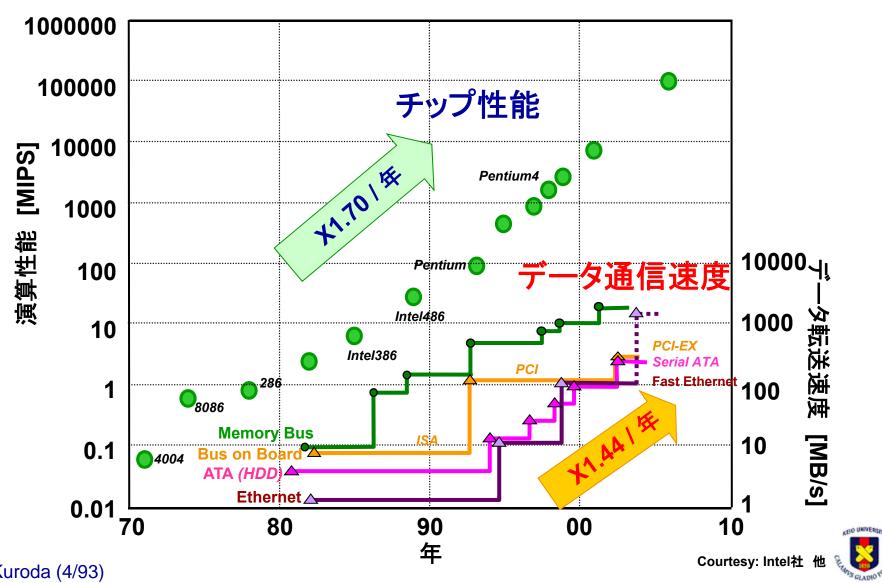

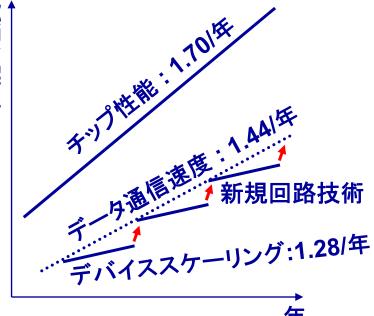

### チップ性能とデータ通信速度

70%向上したチップ性能を活用するためにはデータ通信速度の44%向上が必要

#### チップ性能は面に比例、通信速度は辺に比例

- ■チップ性能

- 1.15 (トランジスタの動作速度) x 1.49 (集積度) = x1.70/年 面(チップ全面に集積できるから)

- ■データ通信速度

- 1.15 (トランジスタの動作速度) x 1.11 (I/O数) = x1.28/年 辺(周辺だけから出入りするから)

通信速度 ∝辺(I/O数)

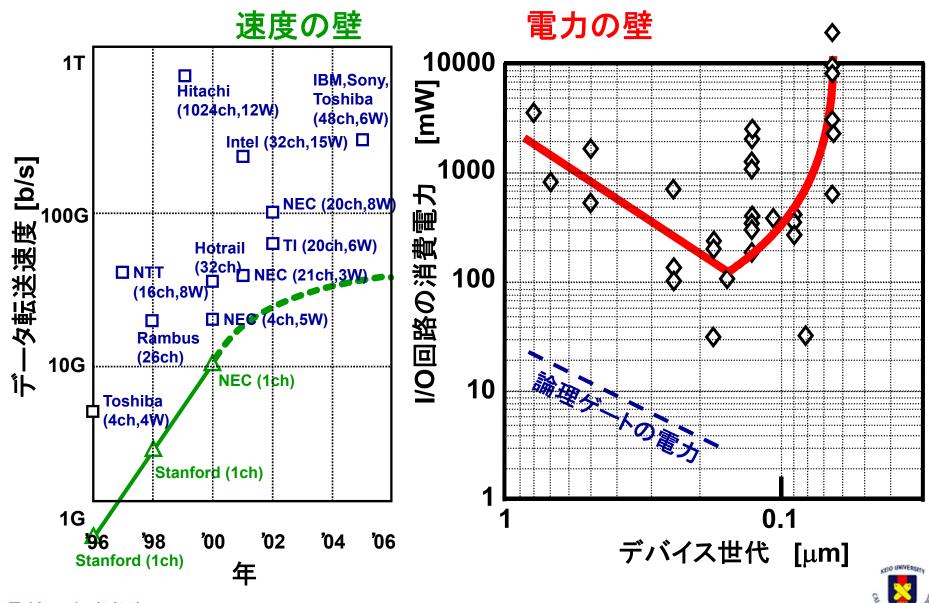

### チップ間データ通信速度の改善は限界

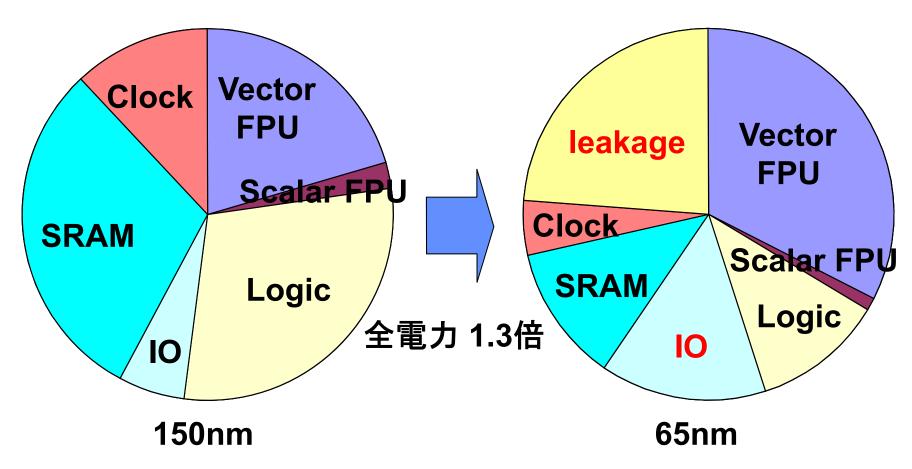

### 急増する通信電力

スーパーコンピュータ用チップの電力内訳

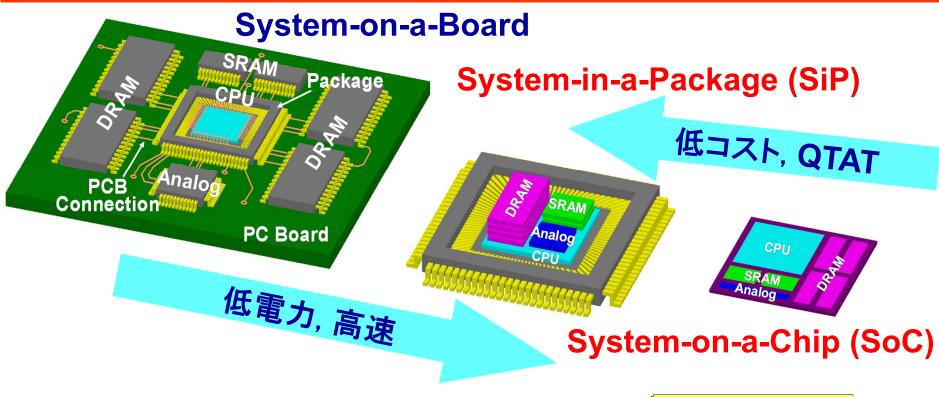

#### **SiP**

出典: EE Times

出典: Intel

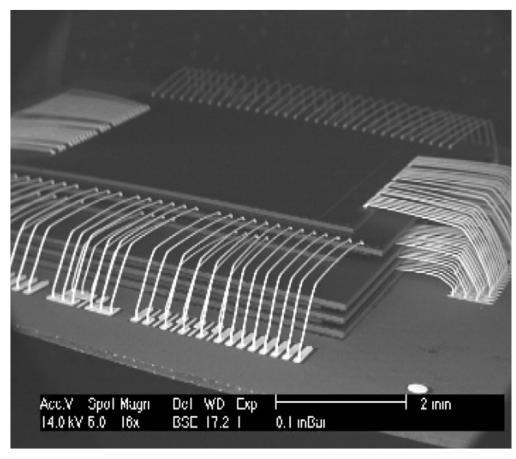

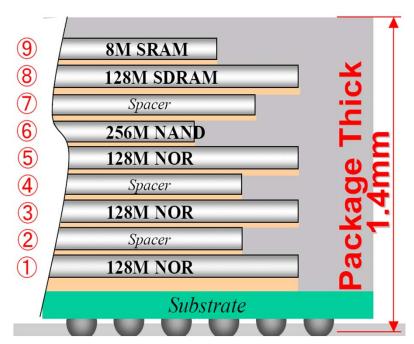

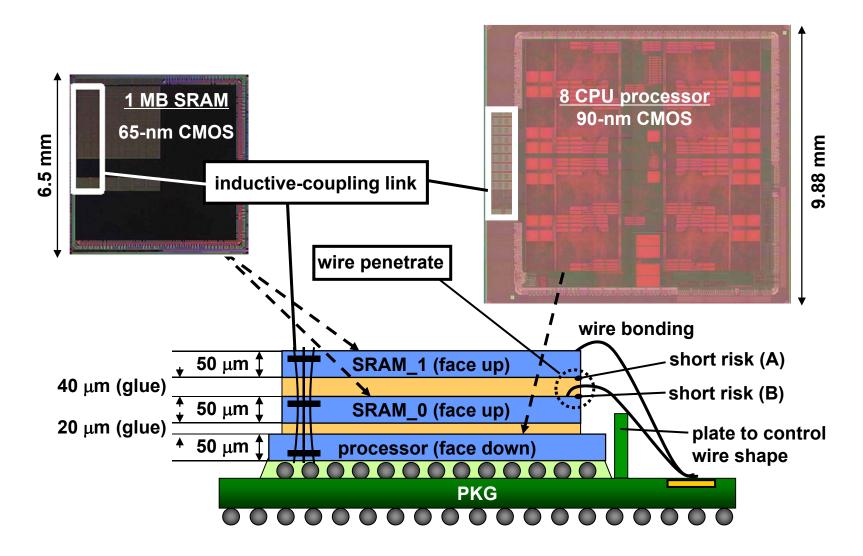

## 積層チップをワイヤボンディングで配線

Courtesy: 東芝

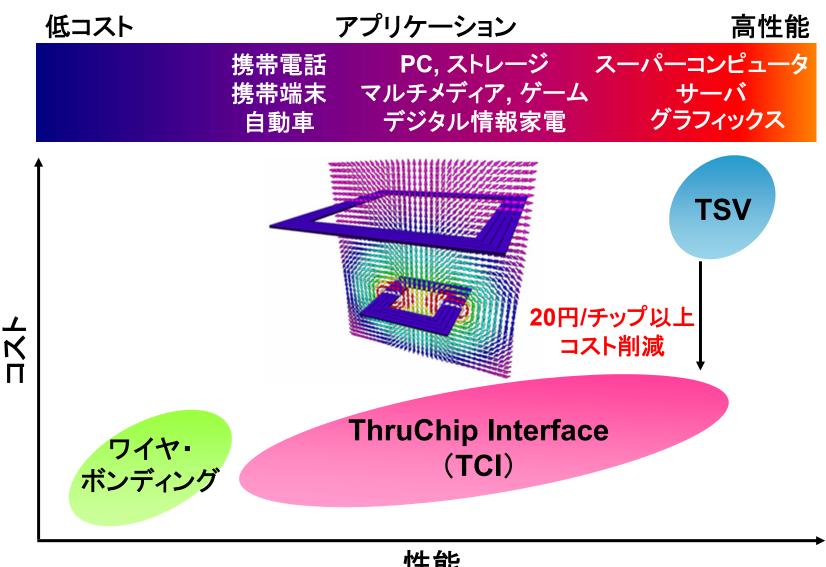

#### 周辺から面へ、機械式から電子式へ

- Chip Performance ∝Area (Tr.#) Pin Bandwidth ■ ∞Periphery (I/O#) ■ . . . . . . . . . .

- (+) 低コスト (-) 低バンド幅

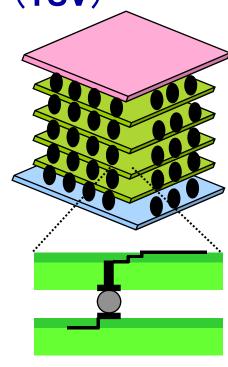

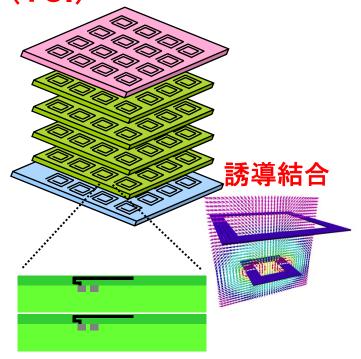

(TSV)

- (+) 高バンド幅

- (-) 高価

- 低信頼性

■ ワイヤボンディング ■Through Si Via ■ThruChip Interface (TCI)

- (+) 高バンド幅

- (+) 低コスト

- (+) 高信頼性

- (+) 薄化

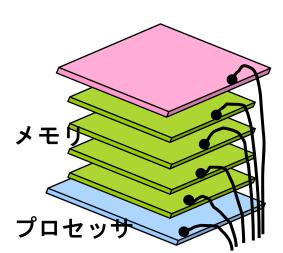

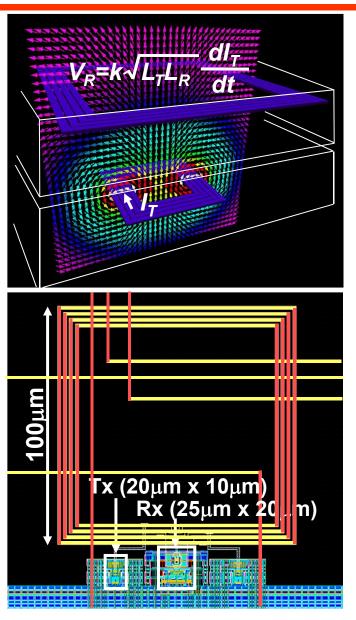

### **ThruChip Interface (TCI)**

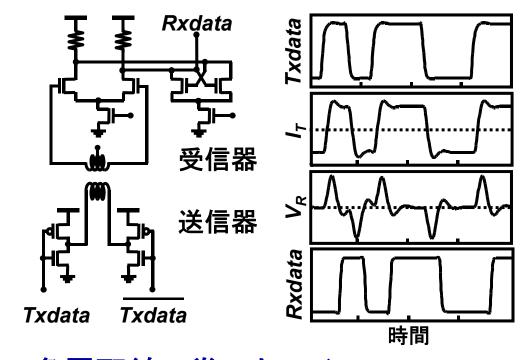

- ■誘導結合通信

- デジタルCMOS回路

- 多層配線で巻いたコイル

- ロジック配線がコイルを通過できる

- コイルはチップのどこにでも配置できる (SRAMセル上でも構わない)

© T. Kuroda (11/93)

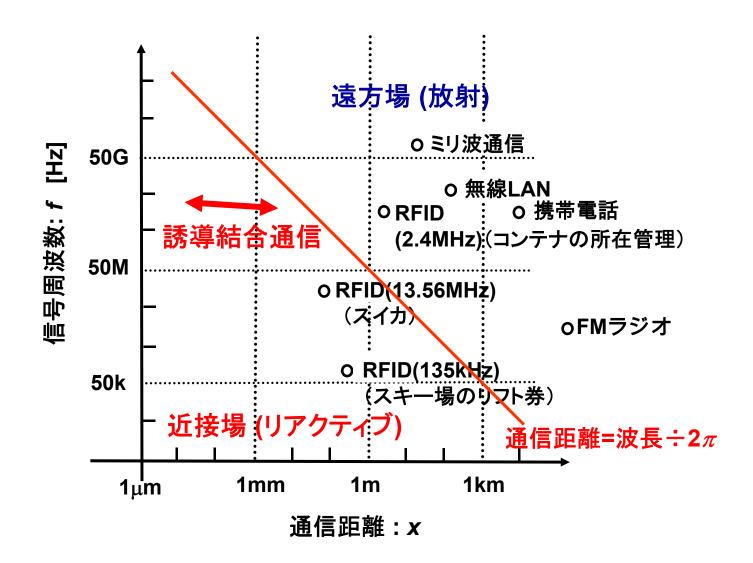

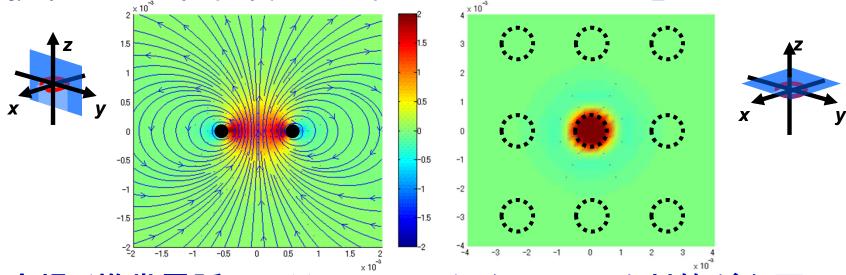

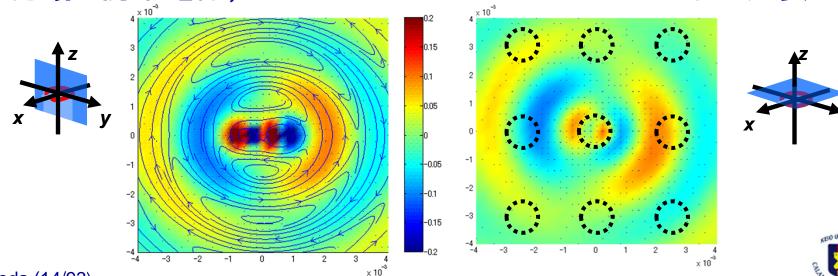

#### 近接場と遠方場

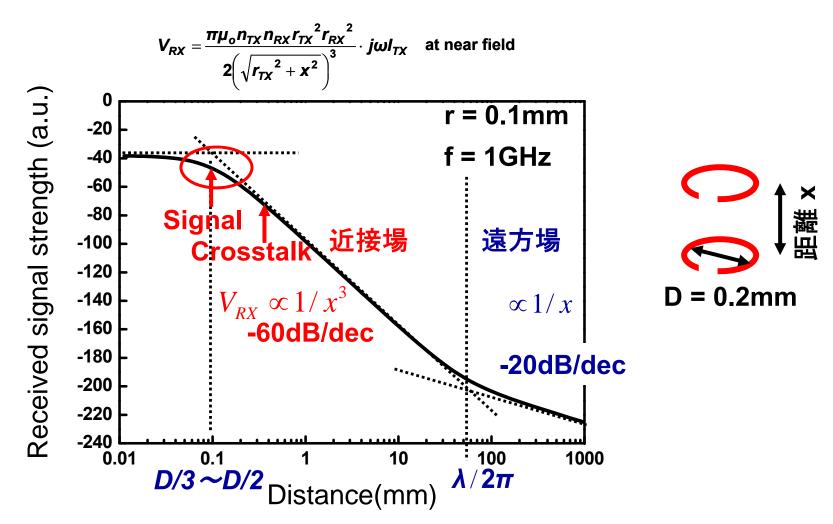

#### 近接場での信号減衰

近接場でコイルの半径以上の通信距離になると信号は急速に減衰する。

#### 近接場の電磁界

■ 近接場 (TCI): 高密度に面配置してもクロストークを生じない

■ 遠方場 (携帯電話, ワイヤレスLAN): クロストーク対策が必要

#### 高速、低電力、薄い

#### ■高速

ISSCC'04 1.2Gb/s

ISSCC'05 200Gb/s

ISSCC'06 1Tb/s (1000ch)

ISSCC'08 11Gb/s/ch

ISSCC'10 (24.3) 8Tb/s (1000ch)

TSV:

バンプ必要

● チャネル数を増やすことで総データ転送速度を高くできる.

#### ■低電力

VLSI'06 ISSCC'07A-SSCC'08VLSI' 10 4.3pJ/b 0.14pJ/b 0.065pJ/b 0.01pJ/b

H.264/AVC: 0.1pJ/b\*23.1Gb/s=2.3mW

●ESD保護回路 (3pJ/b) 不要.

#### ■ 薄い、熱抵抗低い

TCI: バンプ不要

バンプ不要

バンプ必要

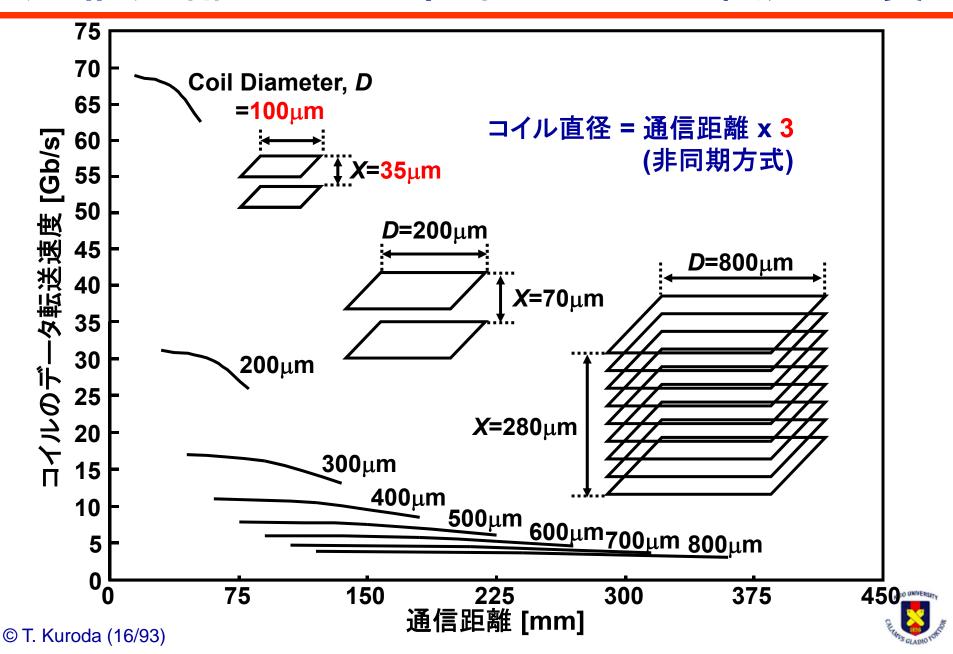

### 通信距離とコイル直径とデータ転送速度

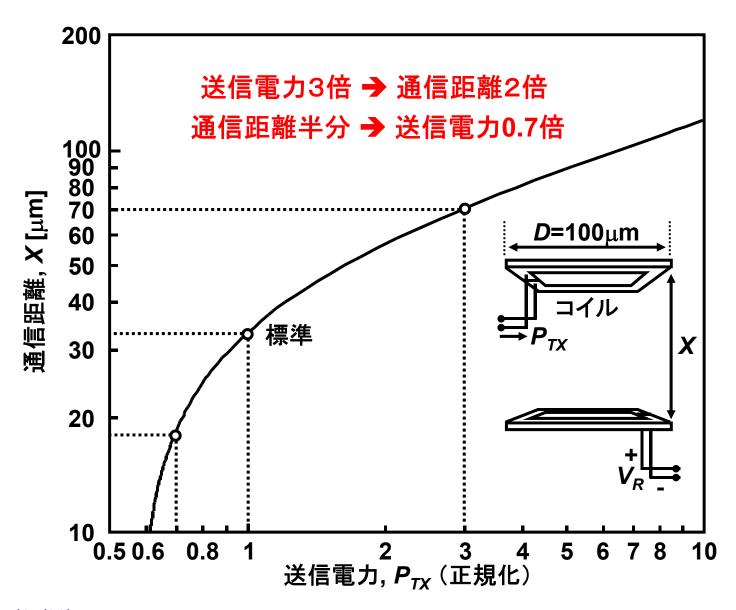

#### 送信電力と通信距離

## 同期方式と非同期方式

|           | 同期方式                                 | 非同期方式                                                      |

|-----------|--------------------------------------|------------------------------------------------------------|

| 回路        | Txclk パルス 生成 サイング サイング アントローラ Rxdata | Txdata $ \begin{array}{cccccccccccccccccccccccccccccccccc$ |

| 転送速度      | 5Gb/s                                | 11Gb/s                                                     |

| エネルギー/bit | 0.3pJ/b                              | 1pJ/b                                                      |

| タイミング制御   | 必要                                   | 不要                                                         |

| コイル直径     | 通信距離 x 2                             | 通信距離 x 3                                                   |

in 0.18μm CMOS

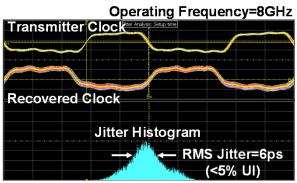

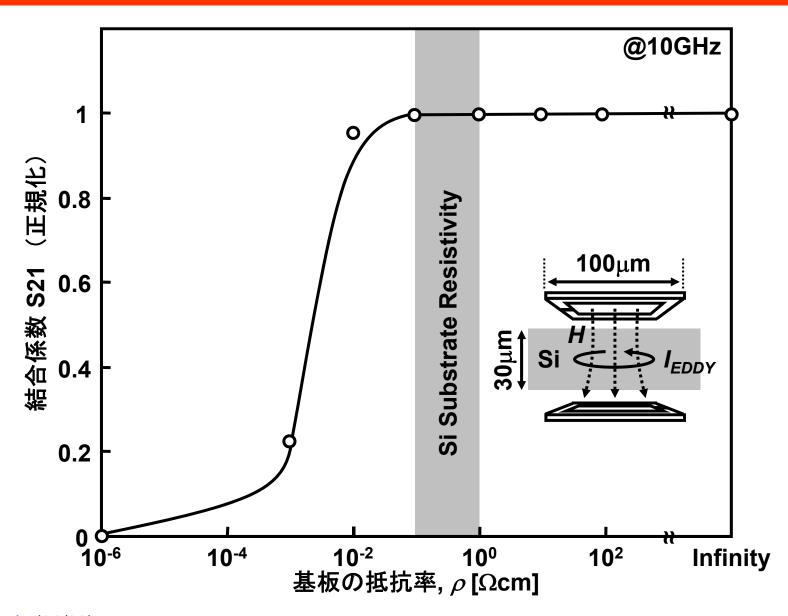

#### 信頼性

- ビット誤り率 BER < 10<sup>-14</sup> 従来の有線通信と同程度 [ISSCC'04]

- ジッター < 5% UI

- 結合劣化

シリコン基板での渦電流

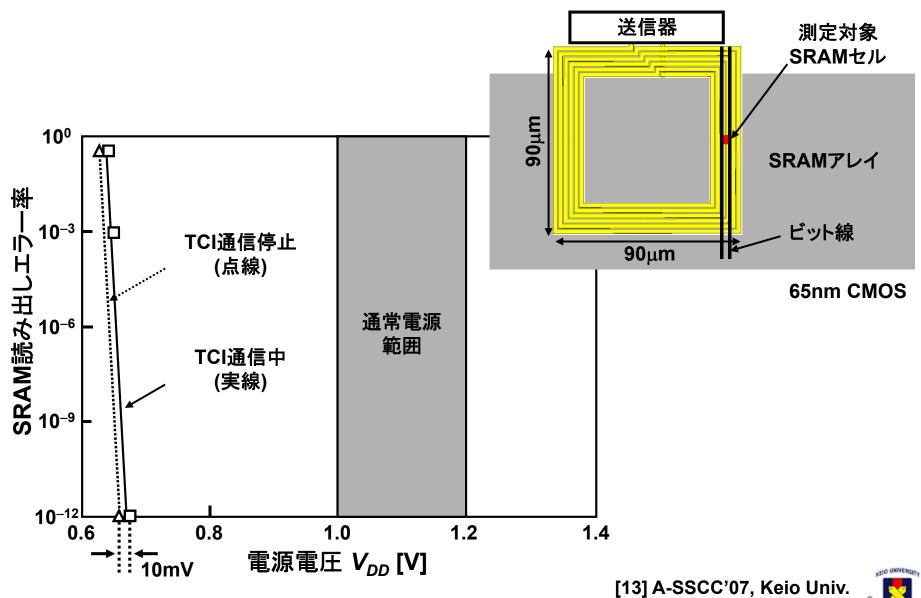

電源線網での渦電流 [A-SSCC'07]

ビット線/ワード線での渦電流 [ISSCC'10]

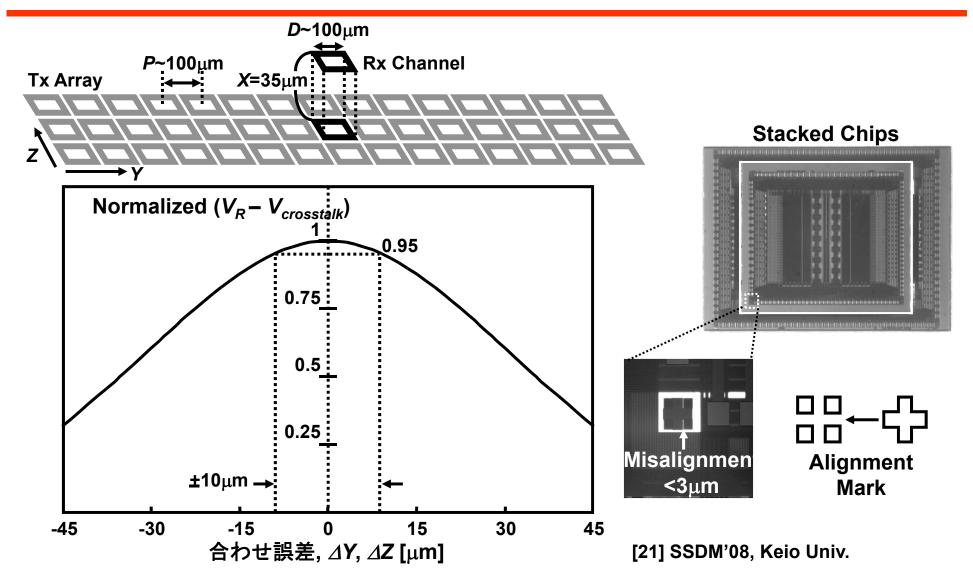

チップ位置合わせ誤差 [SSDM'08]

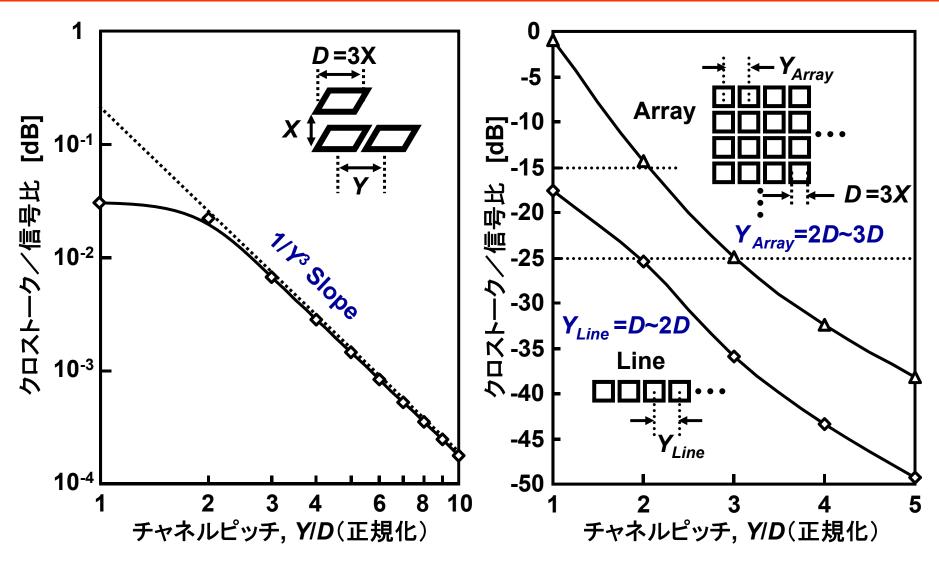

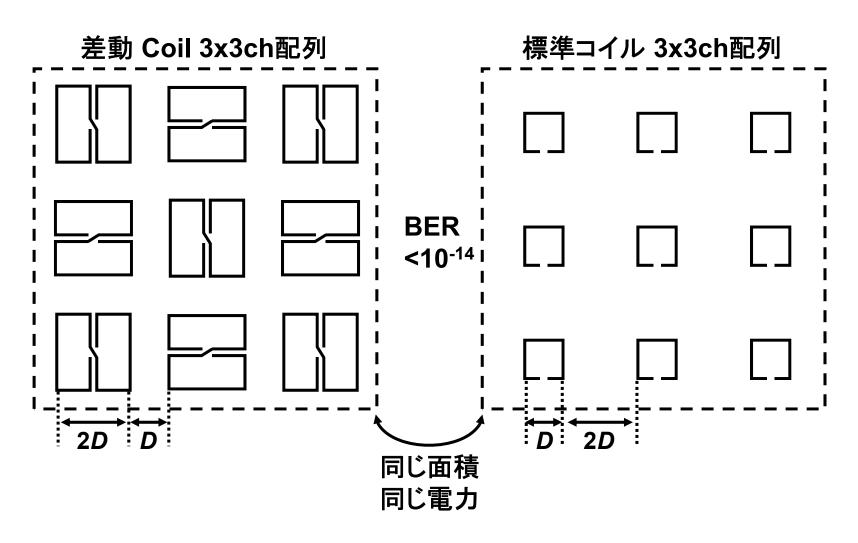

- チャネル間クロストーク ピッチ > 直径の2倍 [CICC'04]

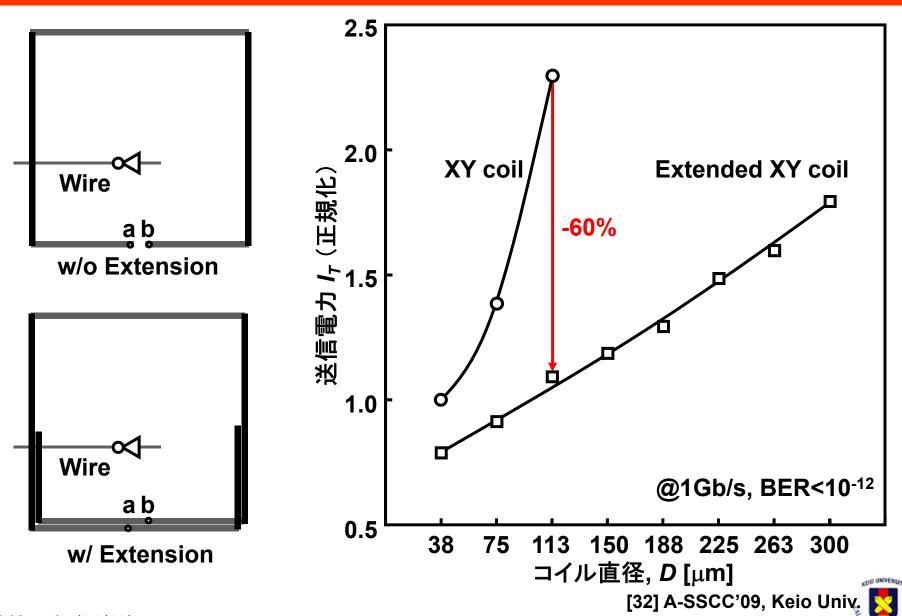

- 干渉 デジタルからTCIへ [A-SSCC'09] TCIからSRAMへ [A-SSCC'07] 環境からTCIへ (EMS) [SSDM'09] TCIから環境へ (EMI) [SSDM'09]

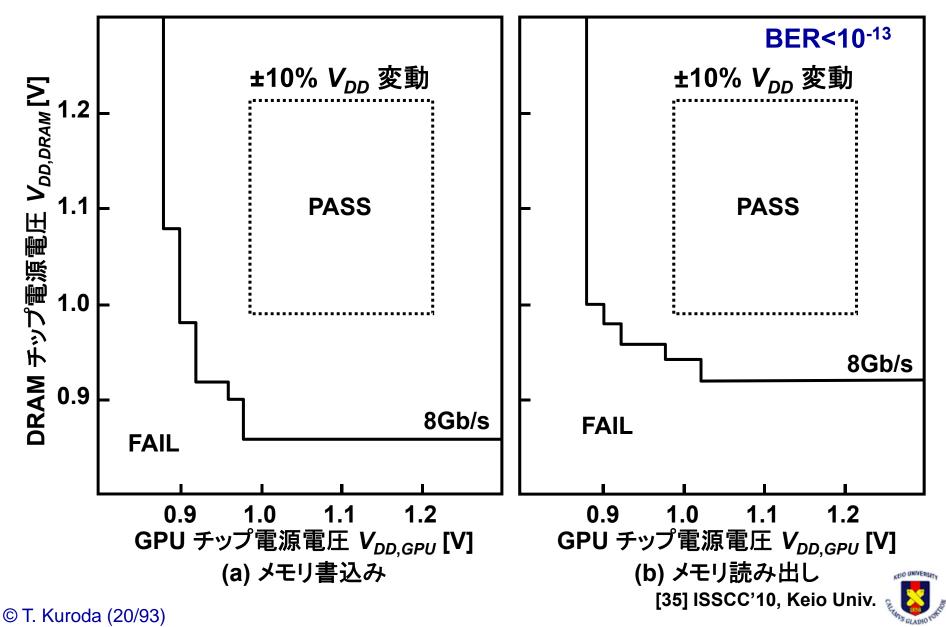

## VDDばらつき耐性

### シリコン基板による遮断効果

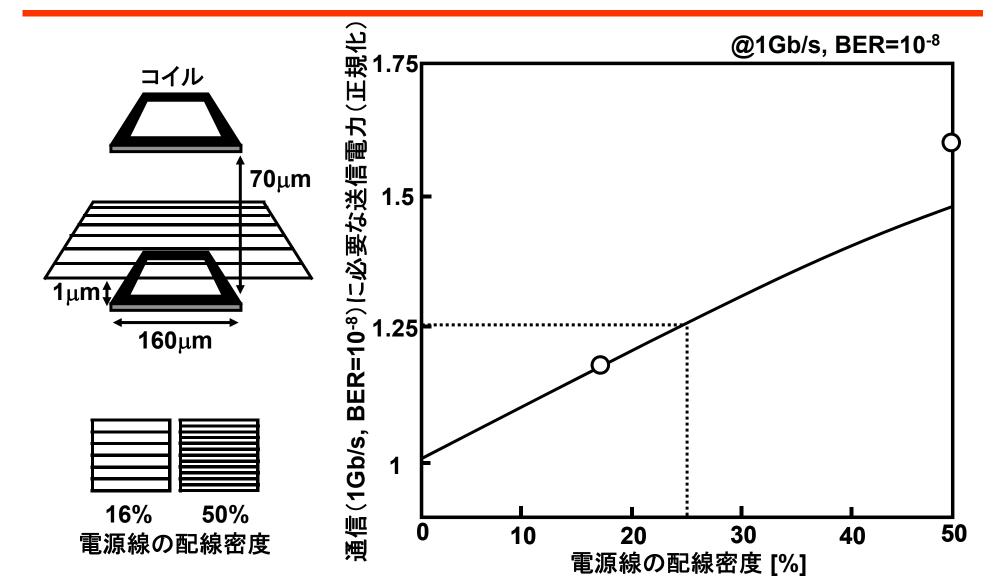

#### 電源線による遮断効果

[13] A-SSCC'07, Keio Univ.

### ビット線・ワード線による遮断効果

### チップの位置合わせ耐性

・コイルサイズの±10%(典型的には±10mm)の合せ誤差でも問題なし

## チャネルピッチとクロストーク

[3] CICC'04, Keio Univ.

### デジタル配線からのノイズ耐性

### SRAMビット線上にコイル配置

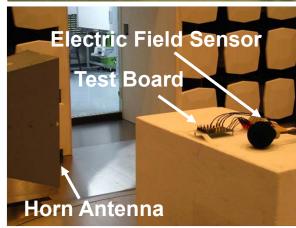

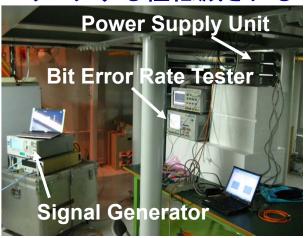

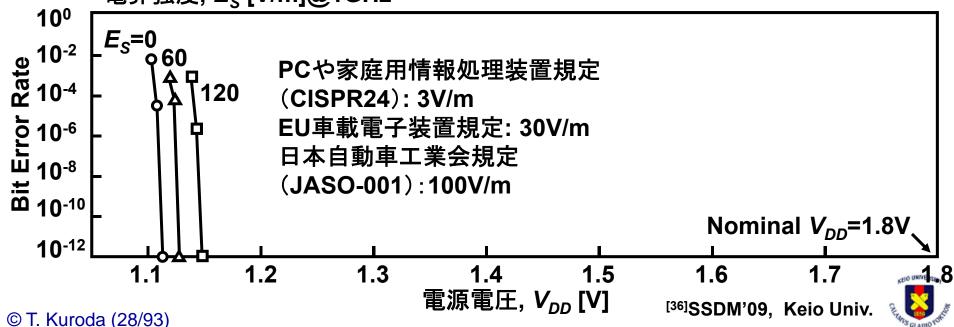

## 電磁妨害耐量(EMS)

■環境ノイズの影響: 問題なし, スケーリングする程低減される

電界強度, E<sub>s</sub> [V/m]@1GHz

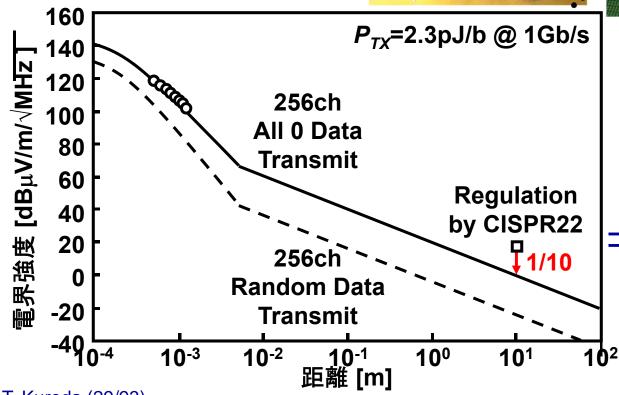

## 不要放射(EMI)

#### ■環境へのノイズ: VCCIの規制値より十分に低い

究極の解決策: 差動方式

コイルを800万個搭載可能

[36]SSDM'09, Keio Univ.

### 差動コイル

[18]A-SSCC'07, Keio Univ.

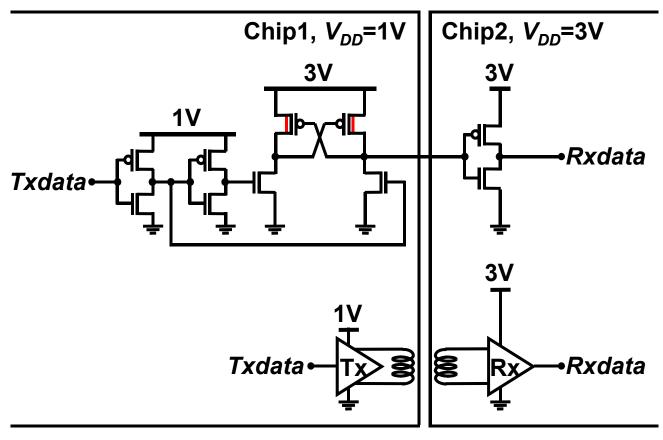

#### AC結合

- ・異なる電源電圧間の信号でもレベルシフトが不要。

- ・厚膜ゲートトランジスタなどが不要でインタフェースが簡単。

- ・バーンインやDVS(低電力のための電源電圧可変)が容易に実現。

[7] ESSCIRC'06, Keio Univ.

#### 低コスト

|         | TCI    | TSV |

|---------|--------|-----|

| プロセス    | 標準CMOS | 新開発 |

| ESD保護回路 | 不要     | 必要  |

| コスト     | 低い     | 高い  |

#### **EMC-3D CoO Goals**

Pilot Line \$241.00 CoO

Production \$162.00 CoO

1.2万円/600チップ=20円/チップ

2007

Capital \$52.0M

Capital \$43.0M

Capital \$32.0M

(2600wspm)

(3800wspm)

(4800wspm)

2008 Goal

2009 Goal

EMC-3D Pan Pac 2007 Symposiun Jan. 29-31, 2007 Page27

SEMITOOL

EMC-3D : TSV promotion community http://www.emc3d.org/

#### TSVと同程度の性能を安く実現

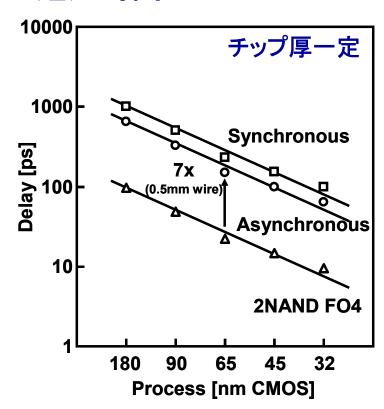

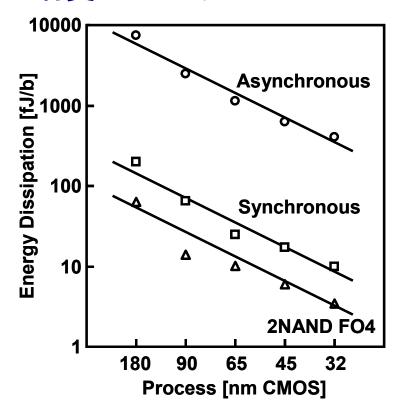

### スケーリングする性能

#### ■ 遅延時間

2NAND FO4 7段~10段 または 0.5mm長配線(65nm)

#### ■ 消費エネルギー

2NAND FO4 4段~80段

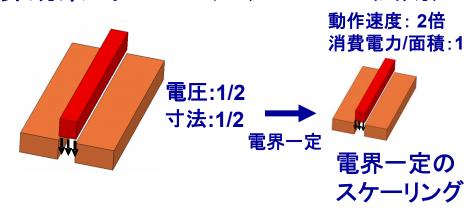

## 3次元スケーリングシナリオ

#### スケーリング:性能・コスト比が指数関数的に改善

■ 電界効果トランジスタ (Mooreの法則)

■ TCI(3次元Mooreの法則)

| データ転送速度/面積: 8f       | 倍  |

|----------------------|----|

| 直径:1/2消費エネルギー/ビット:1/ | /8 |

| 参数:1/1.5             |    |

|                      |    |

| チップ厚:1/2             |    |

|                      | ı  |

| 磁界変化一定のスケールング        |    |

| トランジスタの寸法 [x]                                                          | 1/α            |

|------------------------------------------------------------------------|----------------|

| 電源電圧 [V]                                                               | 1/α            |

| チップの厚さ [7]                                                             | 1/α            |

| コイルの巻き数(配線総数) [n]                                                      | $\alpha^{0.5}$ |

| 電流 [/]                                                                 | 1/α            |

| 回路の遅延時間 [f]~[CV/I]                                                     | 1/α            |

| コイルの直径 [ <i>D</i> ]~[1/x]                                              | 1/α            |

| 自己インダクタンス [L]~[n <sup>2</sup> D]                                       | 1              |

| 磁界の結合定数 [k]                                                            | 1              |

| 受信信号 [ <i>v<sub>R</sub></i> ]~[ <i>kn</i> <sup>2</sup> <i>D(l/t)</i> ] | 1              |

| クロストーク [v <sub>RS</sub> /v <sub>RN</sub> ]                             | 1              |

| データ転送速度 / チャネル [1/f]                                                   | ಶ              |

| チャネル数 / 面積 [1/D²]                                                      | $\alpha^2$     |

| 総データ転送速度 / 面積 [1/tD <sup>2</sup> ]                                     | $\alpha^3$     |

| 消費エネルギー / ビット [/tV]                                                    | 1/α³           |

[7] ESSCIRC'06, Keio Univ.

### 研究成果

#### ■ ISSCCで14論文

ISSCC'04 ISSCC'05 ISSCC'06 ISSCC'07 ISSCC'07 ISSCC'08 ISSCC'09 ISSCC'09 ISSCC'10 ISSCC'10 ISSCC'10

#### ■ CICCで3論文

■ VLSI回路シンポジウムで8論文

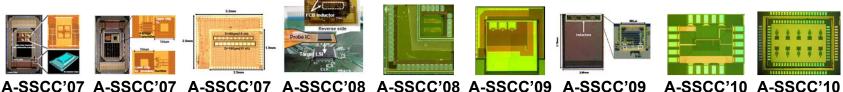

#### ■ A-SSCCで9論文

A-SSCC'07 A-SSCC'07 A-SSCC'07 A-SSCC'08 A-SSCC'08 A-SSCC'09 A-SSCC'09

### 内容

- 1. 磁界結合によるチップ間通信 ThruChip Interface (TCI)

- 2. TCIの応用

- 3. 電磁界結合によるボード間通信 Coupled Transmission Line (CTL)

チップレベル 3D IC μm, 5Tbps, TCI

ボードレベル 非接触コネクタ mm, 50Gbps, CTL

### 実用化研究

### ■8年間の基礎研究を終え実用段階

ISSCC'09

ISSCC'10

ISSCC'09, VLSI'09

ISSCC'10

**VLSI'09**

積層メモリ

プロセッサ・メモリ高速リンク

積層プロセッサ

ISSCC'10

VLSI'09

ISSCC'09

ISSCC'07, A-SSCC'08

VLSI'09

非接触メモリ

非接触ウェハテスト バスプローブ インタポーザ

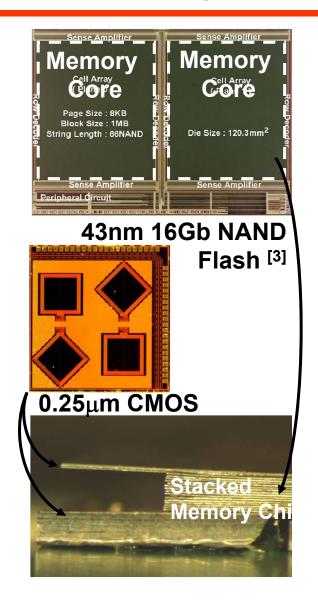

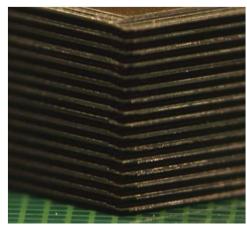

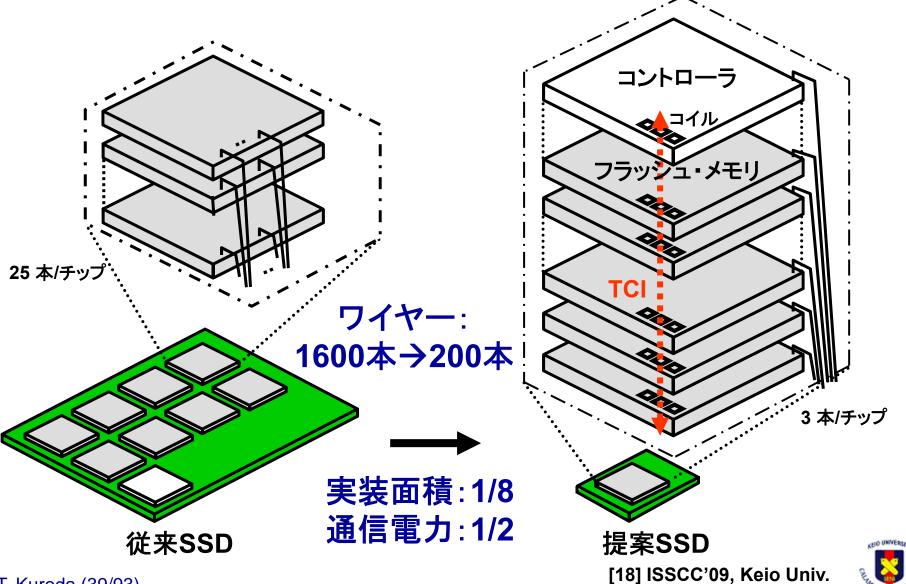

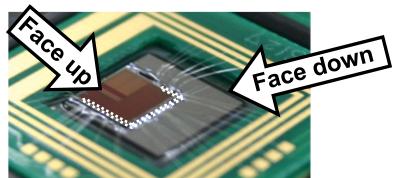

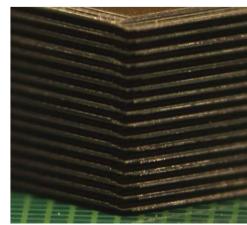

### メモリの積層:SSD応用

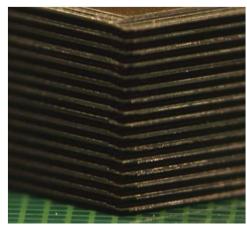

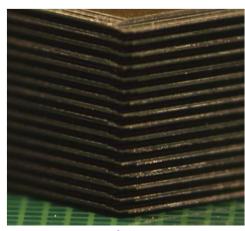

1つのパッケージに8枚のチップを積層 1つのパッケージに65枚のチップを積層

© T. Kuroda (39/93)

# ランダムアクセスに成功

|                   | Proposed                                  | Conventional                    |  |

|-------------------|-------------------------------------------|---------------------------------|--|

| Interconnect      | inductive                                 | Wire                            |  |

| Transmission      | Relayed Transmission Broadcast            |                                 |  |

| Power dissipation | <b>307mW</b> (1)                          | 557mW (2)                       |  |

| Wire              | 3 wires                                   | 25 wires                        |  |

| I/O circuit area  | 3,645μm²/chip (1) 145,744μm²/chip         |                                 |  |

| Stacking          | Half-turned-and-<br>staggered stacking    |                                 |  |

| Stacked chips     | 64chips/package 8chips/package            |                                 |  |

| Packages          | 1                                         | 8                               |  |

| Channels          | 2 (Odd/Even)                              | 2                               |  |

| Data rate         | 640Mb/s<br>(< 1inductor x 2Gb/s/inductor) | 640Mb/s<br>(16pin x 40Mb/s/pin) |  |

**NAND Stacking for SSD 180nm**

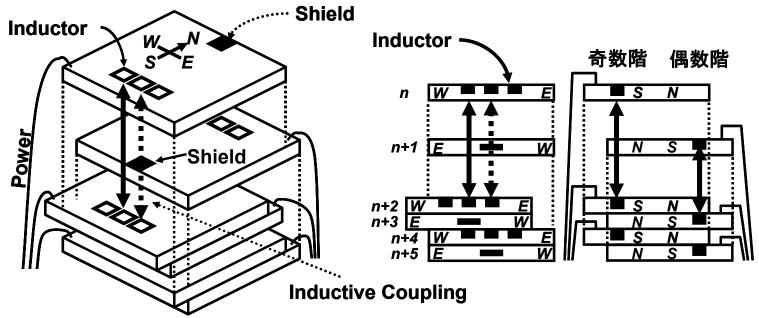

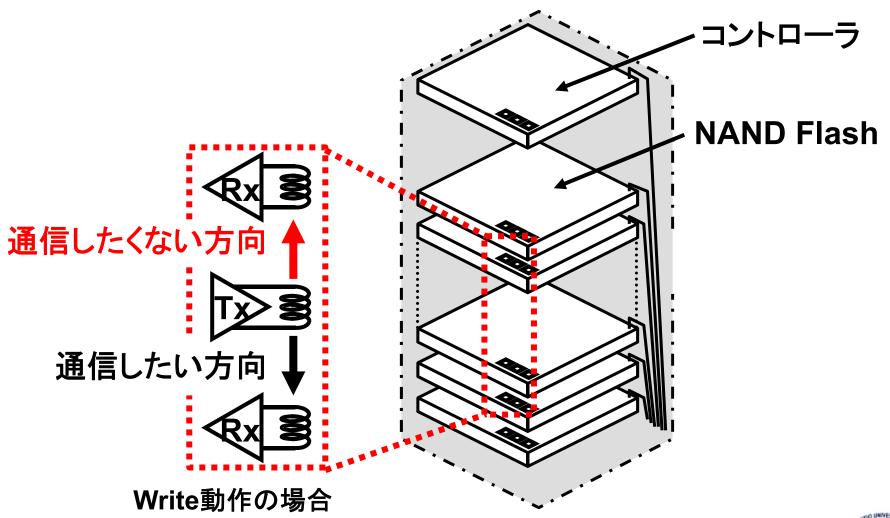

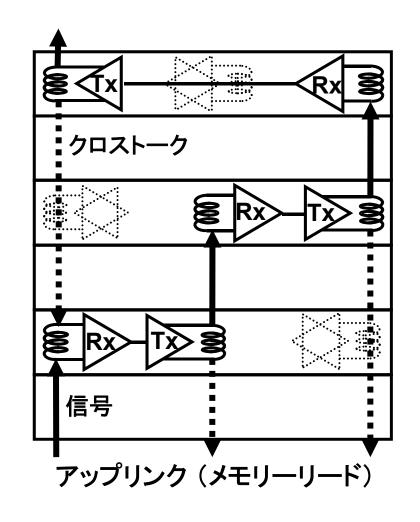

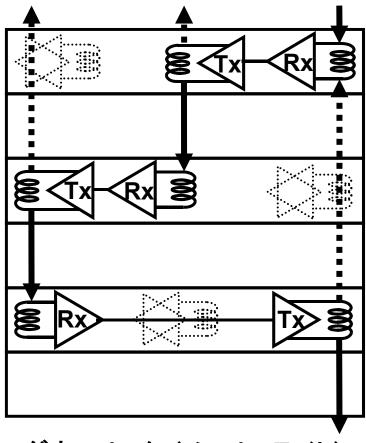

## メモリ積層でのデータ転送方向

■ 同一チップ積層でのデータ転送方向

# 3つのコイルでデータ転送

ダウンリンク (メモリーライト)

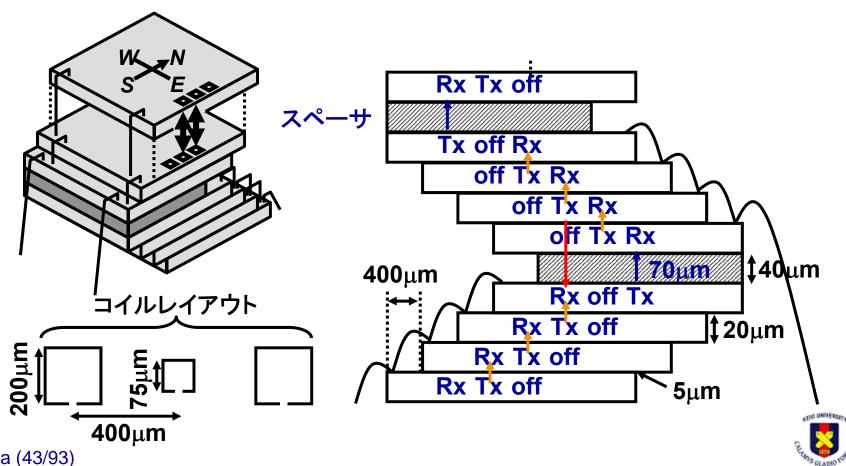

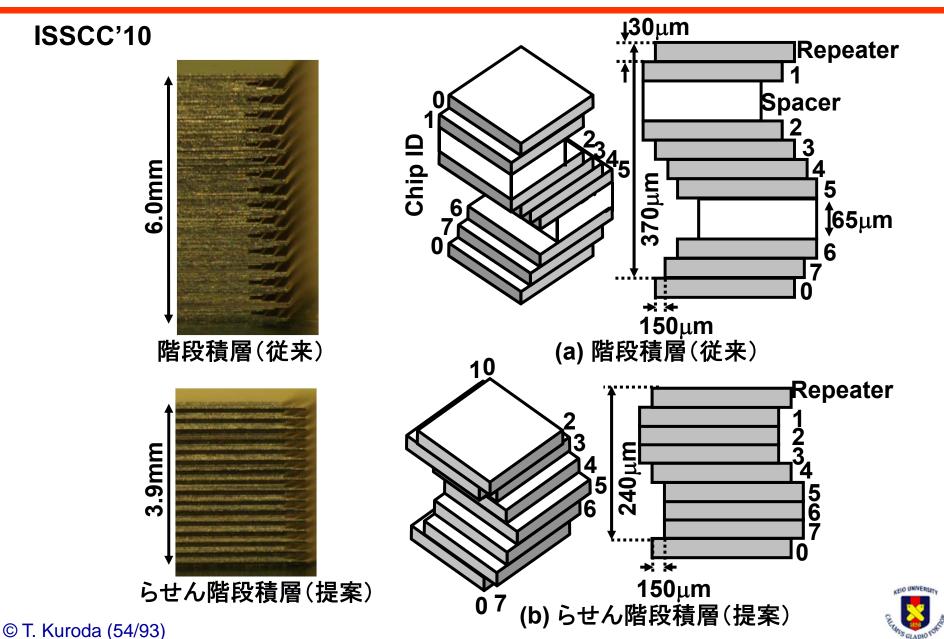

### 階段積層方式

- 電源ボンディングワイヤとコイル位置重ねを両立

- □ずらして積層することでボンディング用空間を確保

- □4チップごとにスペーサーを入れてずらす方向を戻す

- ロチップの重なった部分でボンディングするのでチップを薄くし易い

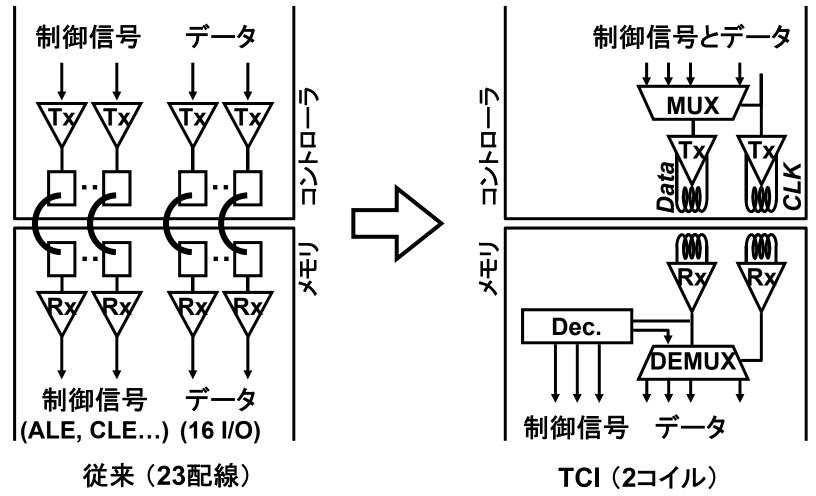

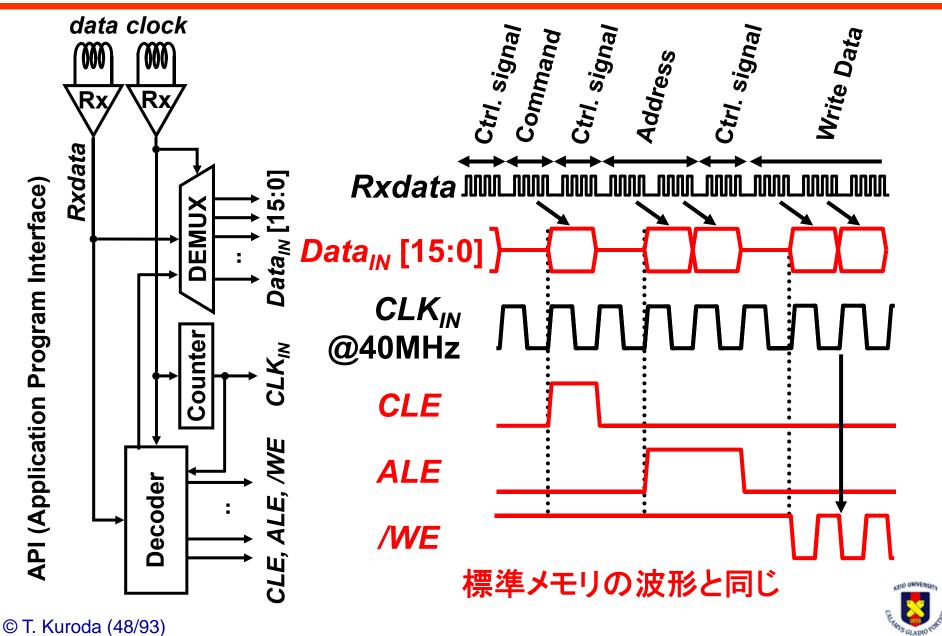

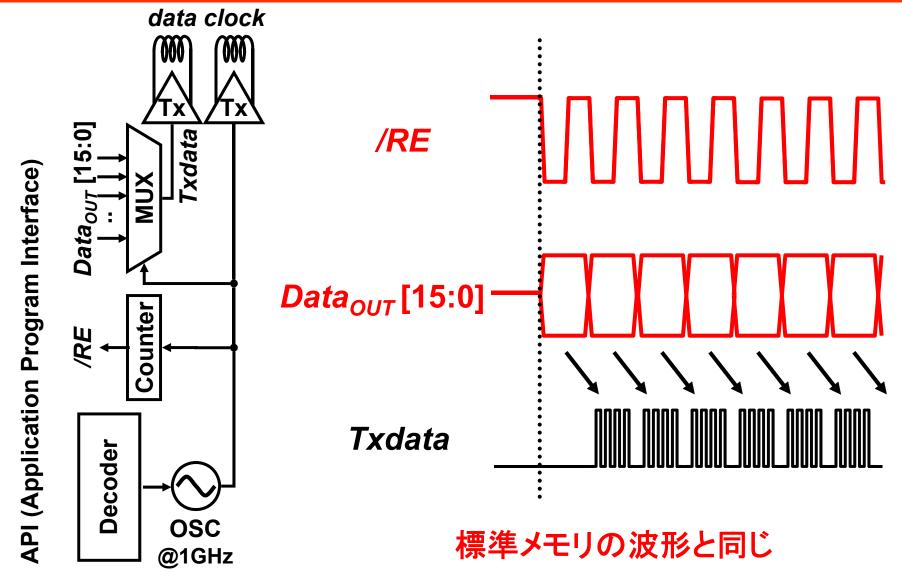

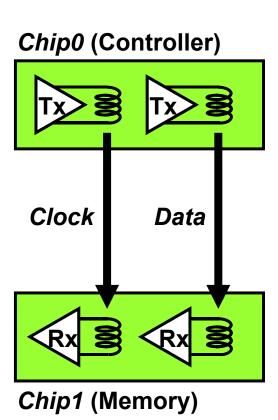

### パケット通信

- 制御信号とデータをパケットでまとめる

- MUX/DEMUX: コイル数削減

### バーストデータ転送

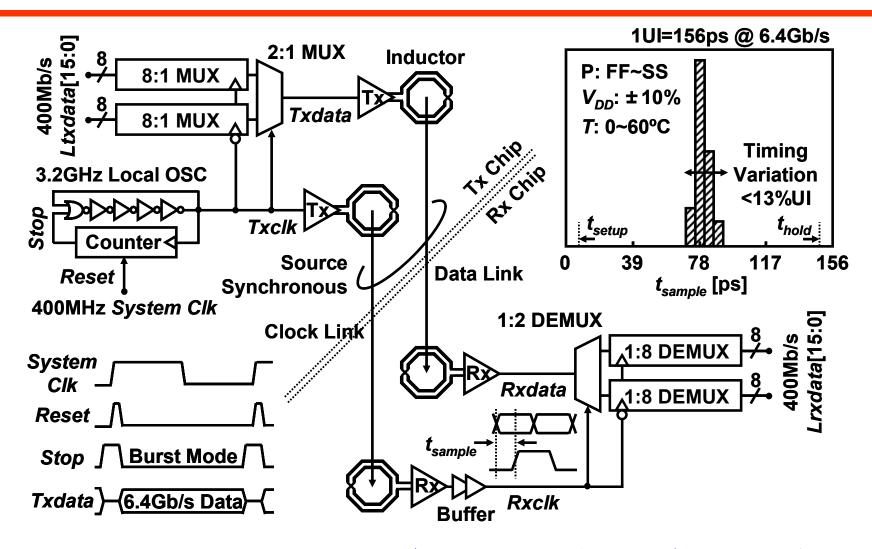

400MHzのクロックでPLL/DLLを用いずに11Gb/sのバーストデータ転送が可能

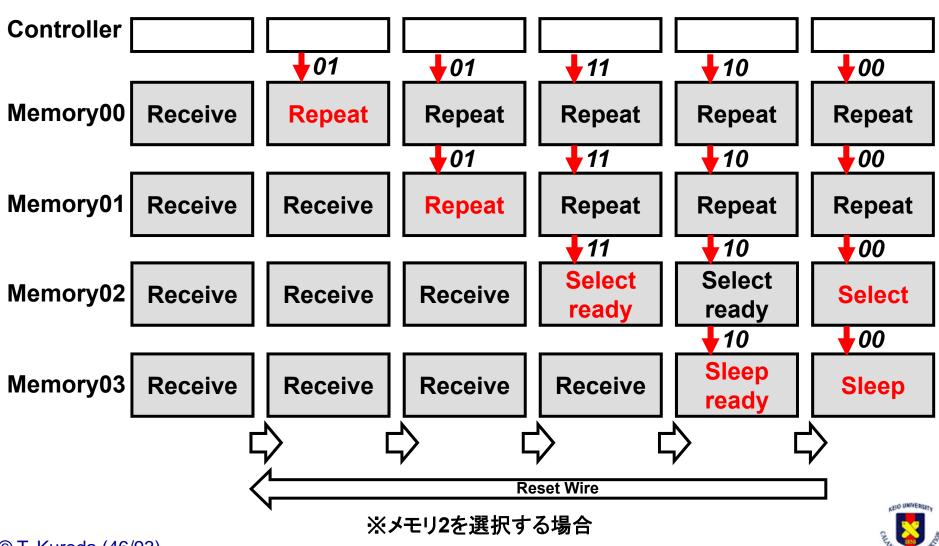

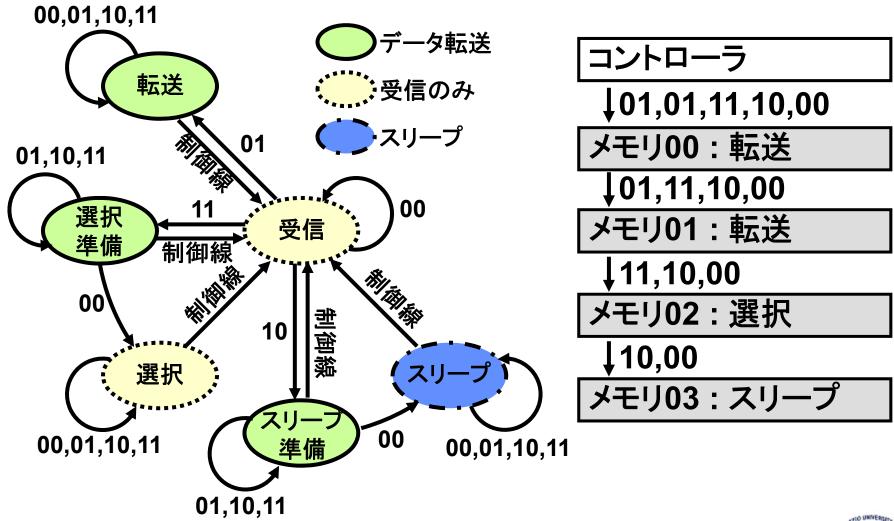

### チップ指定手順

### ■ チップ番号を使用しないため同一チップ積層に最適

### 状態遷移図

### ■ Repeat / Select / Sleep に指定する

### Write動作

### Read動作

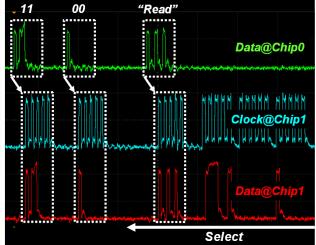

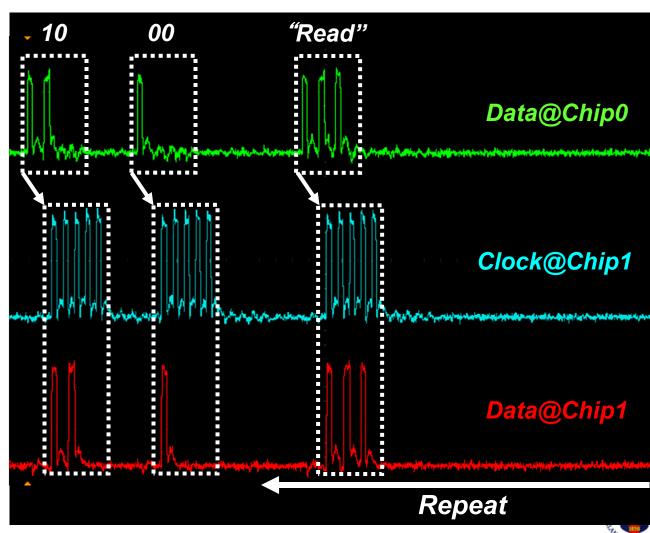

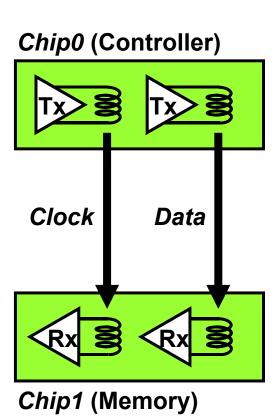

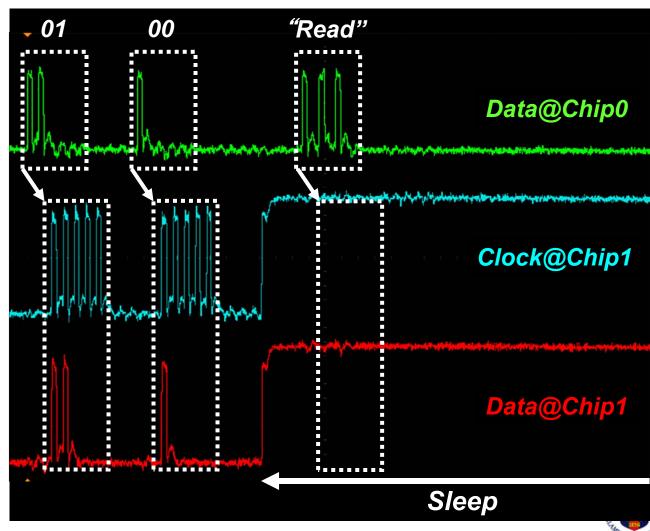

# 測定結果(Repeat)

■ 無線でRepeatに設定

□コマンド(*"Read"*)が受信される

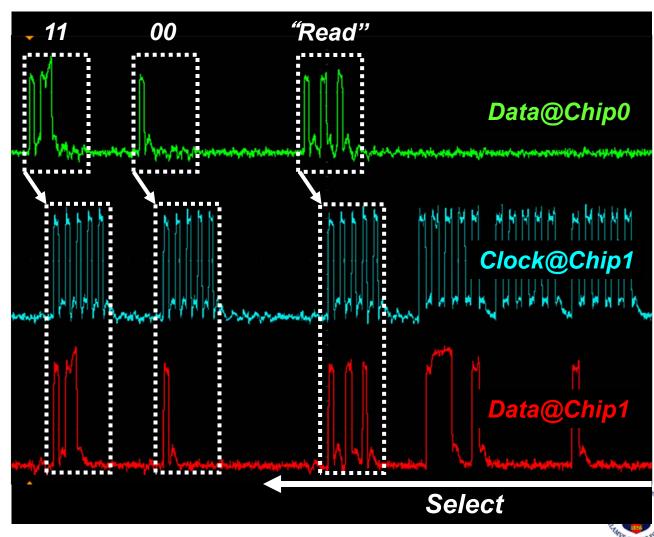

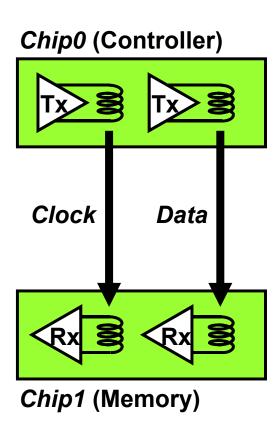

### 測定結果(Select, Read)

■ 無線でSelectに設定

□コマンド( "Read")を元に、データを読出し

# 測定結果(Sleep)

■ 無線でSleepに設定

□コマンド(*"Read"*)が受信されない

# 性能比較

|                  | TCI                   | 従来                                  |

|------------------|-----------------------|-------------------------------------|

| 接続               | 磁界結合                  | 配線                                  |

| 送信               | リレー伝送                 | ブロードキャスト                            |

| 消費電力             | 307mW (1/2)           | 557mW (1)                           |

| I/O 回路面積         | 3,645μm²/chip (1/40)  | 145,744μm²/chip (1)                 |

| チップ数<br>(パッケージ数) | 64<br>(1パッケージx 64チップ) | 64<br>( <mark>8パッケージ</mark> x 8チップ) |

| 通信チャネル           | 2                     | 2                                   |

| データ転送速度          | 640Mb/s               | 640Mb/s                             |

# 128 チップ NANDフラッシュ積層

# 128チップ NANDフラッシュ積層

|                               |                 | TCI                      | 従来                               |

|-------------------------------|-----------------|--------------------------|----------------------------------|

| 接続                            |                 | 磁界結合                     | 配線                               |

| チップ数                          |                 | 128 メモリチップ + 1 コントローラチップ |                                  |

| パッケージ<br>内ボンディ<br>ングワイヤ<br>本数 | チップ間            | 256                      | 2912                             |

|                               | コントローラとパッケージ    | 34                       | 129                              |

|                               | NAND と<br>パッケージ | 257                      | 416                              |

| 送                             | 信               | 8チップ飛ばし                  | 64チップを<br>Wired-ORした<br>ブロードキャスト |

| エネルギー消費<br>[pJ/b/chip]        |                 | 2.6 (0.2)                | 13.6 (1)                         |

| データ転送速度                       |                 | 2Gb/s (3)                | 640Mb/s (1)                      |

[\*] Datasheet : Micron, MT29F8G08FABW

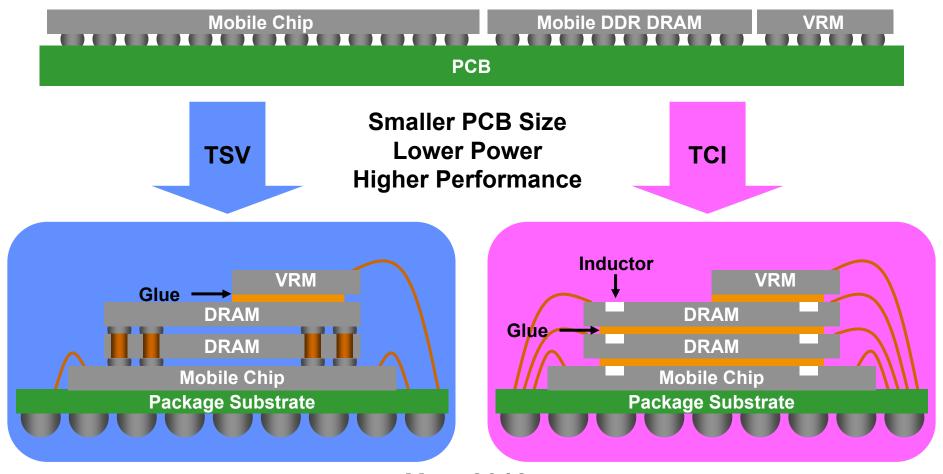

# DRAM積層

|             | グラフィックス                  | モバイル                      |

|-------------|--------------------------|---------------------------|

| データ転送速度     | 256GB/s                  | 8GB/s                     |

| 消費電力        | 10W (1/3)                | 0.1W ( <mark>1/7</mark> ) |

| I/O レイアウト面積 | 0.8mm <sup>2</sup> (1/7) | 0.3mm <sup>2</sup> (1/3)  |

Center-chip wire bonding is available for mass production such as in micro-SD card.

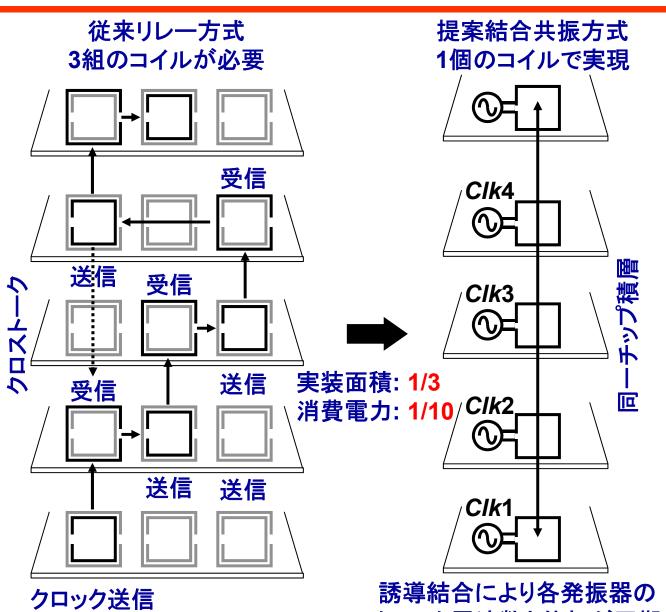

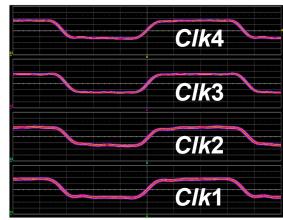

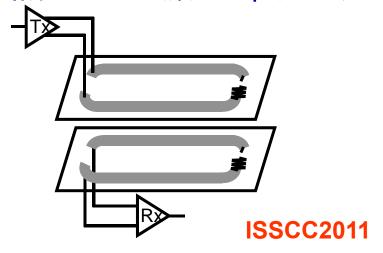

### 3次元クロック分配

クロック周波数と位相が同期

結合共振

Steven Strogatz: SYNC 蔵本由紀: 非線形科学

ISSCC2011

© T. Kuroda (57/93)

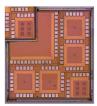

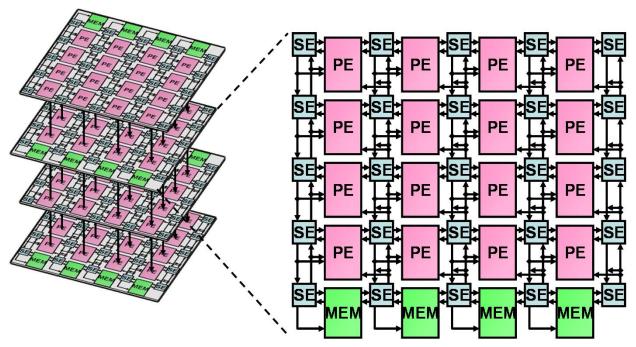

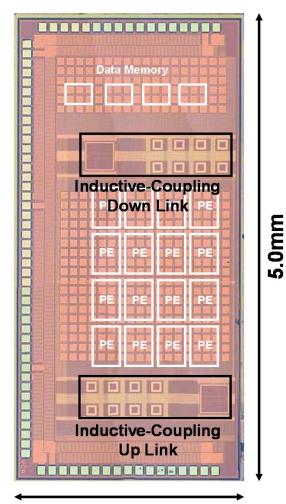

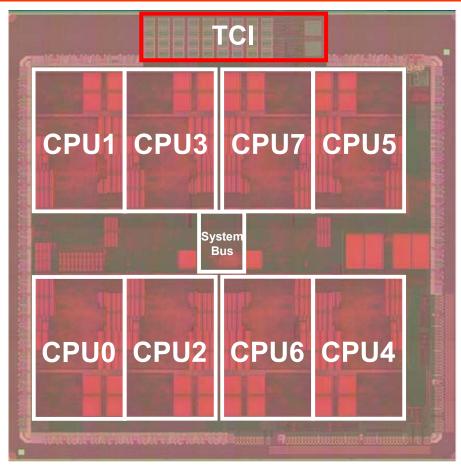

# プロセッサの積層:動的再構成プロセッサ

2.5mm

[22] VLSI'09, Keio Univ.

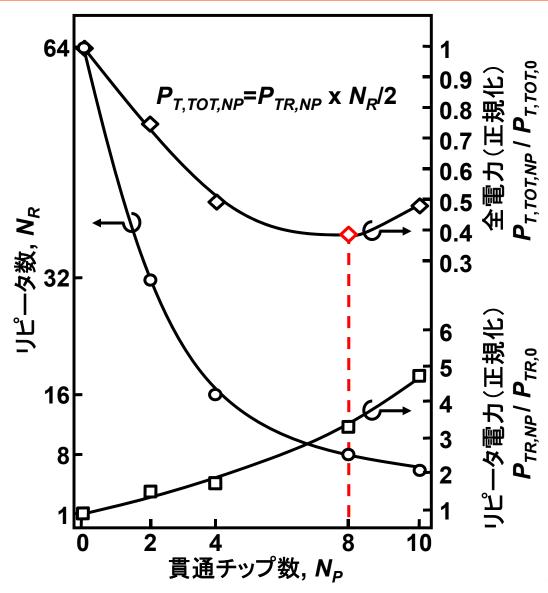

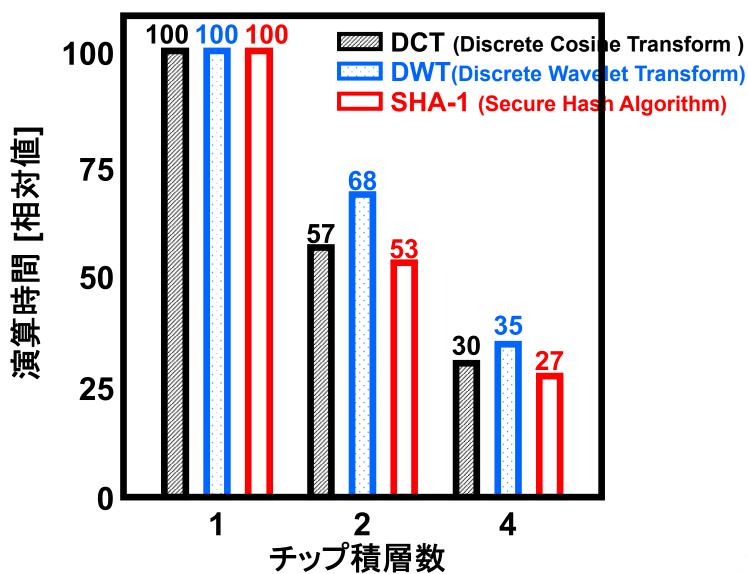

# チップ積層枚数と性能

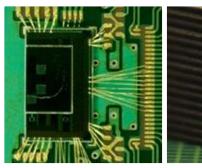

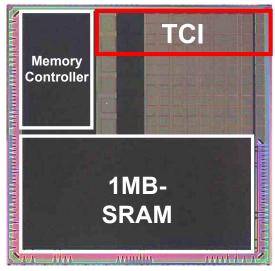

### プロセッサとメモリの結合

SRAM in 65nm CMOS at 1.2V Two SRAM's can be stacked

Processor in 90nm CMOS at 1.0V

エネルギー消費: 1pJ/b (1/30 of DDR2) レイアウト面積: 0.15mm²/Gps (1/3 of DDR2) [27]VLSI'0

[26]ISSCC'09

### 2枚のSRAMと通信

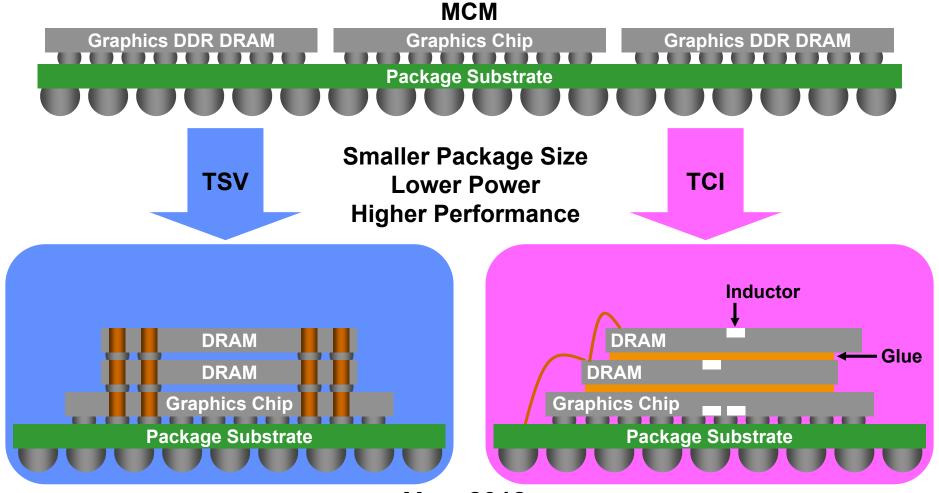

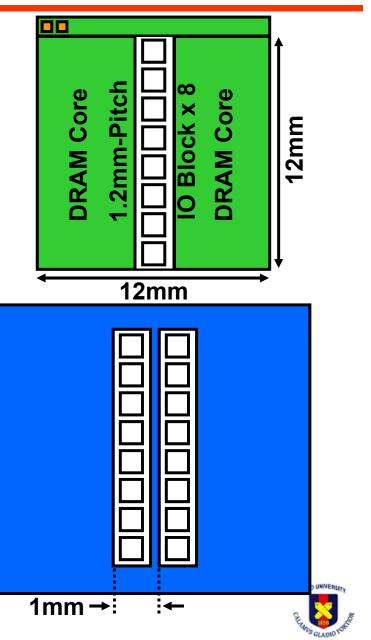

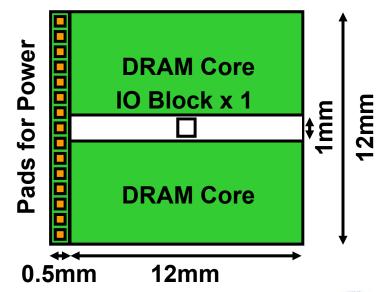

## 高性能グラフィックス用途

**Year 2012**

Capacity Max: 1GB

Bandwidth Max: 256GB/s

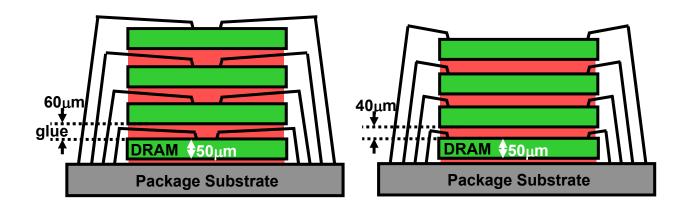

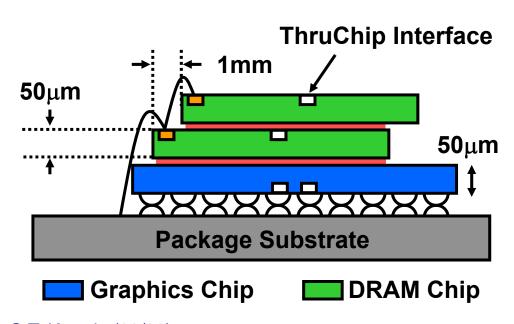

## 256GB/s Graphics Link in 2012

**15mm**

- 36nm 0.5GB DRAM x 2chips = 1GB

- Maximum communication distance

= (50μm + 5μm) x 2 + 50μm = 160μm

- Coil diameter, D = 240μm

Pitch = 480μm, Block size = 700μm

- 32Gb/s x 4 = 16GB/s IO block

16GB/s IO block x 8 x 2chips = 256GB/s

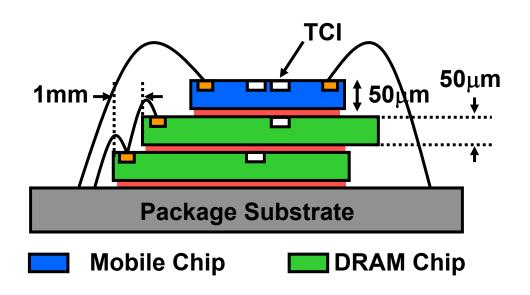

## 低電力携帯用途

**Year 2012**

**Capacity Max: 1GB**

Bandwidth Max: 8GB/s

### 8GB/s Mobile Link 2012

- 36nm 4Gb DRAM x 2 chips = 1GB

- 4GB/s TCl is used for mobile.

- MUX/DEMUX are implemented in CMOS. Energy/bit is reduced to 2pJ/b

- Coil diameter D = 330μm

Pitch = 660μm, Block size = 990μm

- 4GB/s IO block x 2 chips = 8GB/s

# 性能予測(2012年)

|                              |                       | 2012 Graphics                       | 2012 Mobile                |  |

|------------------------------|-----------------------|-------------------------------------|----------------------------|--|

| Number of Stacked DRAM Chips |                       | 2                                   | 2                          |  |

| Data Rate                    |                       | 256GB/s                             | 8GB/s                      |  |

| Chip Thickness               |                       | <b>50</b> μ <b>m</b>                | <b>50</b> μm               |  |

| Power<br>Dissipation         | <sup>[j]</sup> Rambus | 26.6W (1)                           | 920mW (1)                  |  |

|                              | TCI                   | 10.2W ( <mark>1/3</mark> )          | 128mW ( <mark>1/7</mark> ) |  |

| I/O Layout                   | <sup>[j]</sup> Rambus | 5.4mm <sup>2</sup> (1)              | 0.6mm <sup>2</sup> (1)     |  |

| Area in DRAM Chip            | TCI                   | 0.8mm <sup>2</sup> (1/7)            | 0.3mm <sup>2</sup> (1/2)   |  |

| Process                      |                       | 65nm CMOS (Equivalent to 36nm DRAM) |                            |  |

☐ K. Chang, et al., VLSI Cir. 2008

# DRAM高速インタフェースのロードマップ

|                         | 2012          | 2017          | 2022          |

|-------------------------|---------------|---------------|---------------|

| DRAM Process            | 36nm          | 20nm          | 11nm          |

| DRAM Capacity           | 0.5GB/chip    | 2.6GB/chip    | 16GB/chip     |

| Chip Thickness          | <b>40</b> μm  | 35μm          | <b>30</b> μm  |

| Number of Stacked DRAMs | 2             | 2             | 2             |

| Total Memory Capacity   | 1GB           | 6.4GB         | 32GB          |

| Total Memory Bandwidth  | 8GB/s 6       | 48GB/s 6      | 256GB/s       |

| TCI Data Rate           | 1GB/s/ch      | 2GB/s/ch      | 4GB/s/ch      |

| TCI Coil Radius         | <b>150</b> μm | <b>120</b> μm | <b>105</b> μm |

| TCI Channel Number      | 4ch/chip      | 12ch/chip     | 32ch/chip     |

| TCI Energy              | 2pJ/b         | 0.4pJ/b       | 0.08pJ/b      |

| TCI Power               | 128mW         | 153mW         | 164mW         |

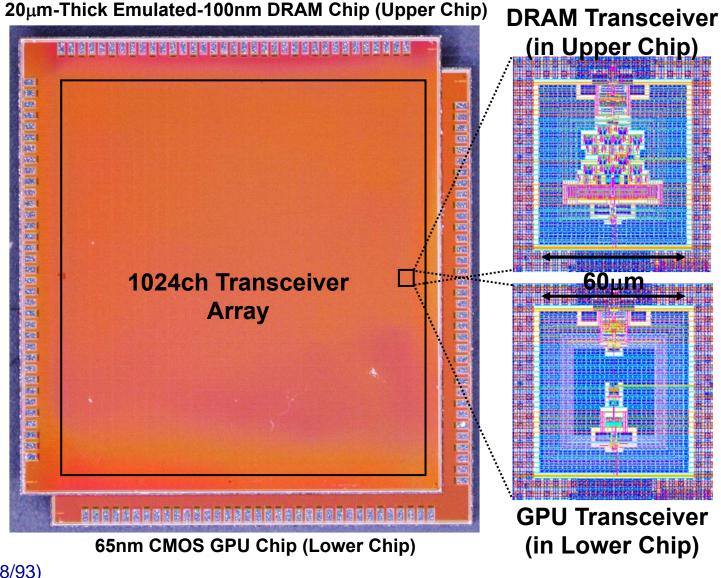

# 1TB/s DRAMインタフェース

#### ISSCC'10

# DRAMインタフェース性能

|             | TCI                             | [1]従来例             |

|-------------|---------------------------------|--------------------|

| 総バンド幅       | 8Tb/s (32)                      | 0.25Tb/s (1)       |

| データ転送速度     | 8Gb/s/Link                      | 16Gb/s/Link        |

| リンク数        | 1024                            | 16                 |

| レイアウト面積     | 6.5mm <sup>2</sup>              | 4.4mm <sup>2</sup> |

| 面積 / バンド幅   | 0.8mm <sup>2</sup> /Tb/s (1/22) | 17.2mm²/Tb/s (1)   |

| 電力消費        | 8W                              | 2W                 |

| エネルギー / bit | 1pJ/b (1/8)                     | 8pJ/b (1)          |

| ビット誤り率      | <10 <sup>-16</sup>              | <10 <sup>-15</sup> |

| プロセス        | 65nm CMOS & Emulated 100nm DRAM | Emulated 40nm DRAM |

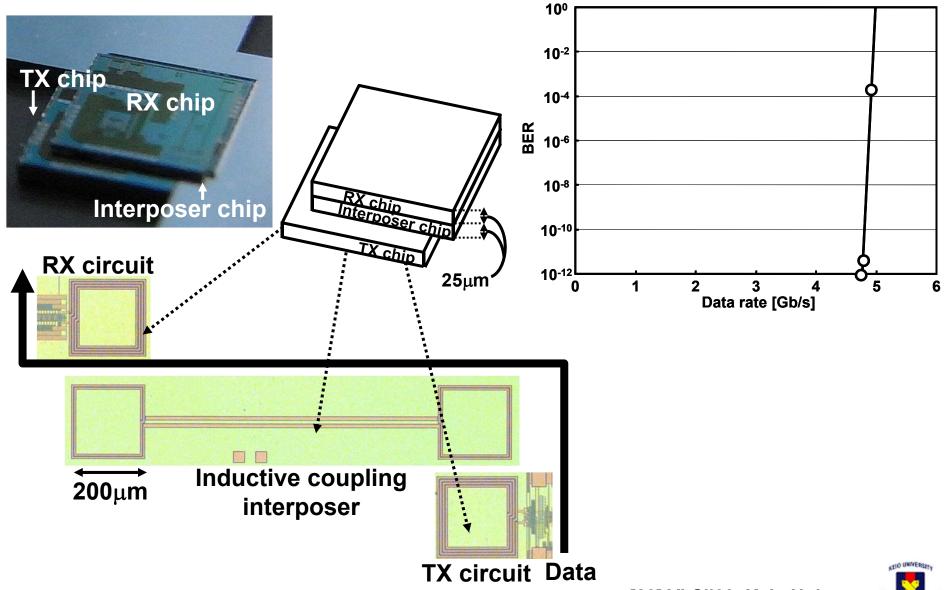

# 誘導結合インタポーザ

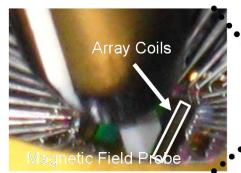

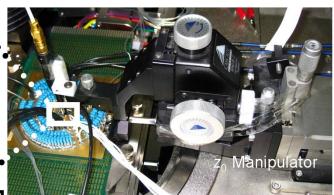

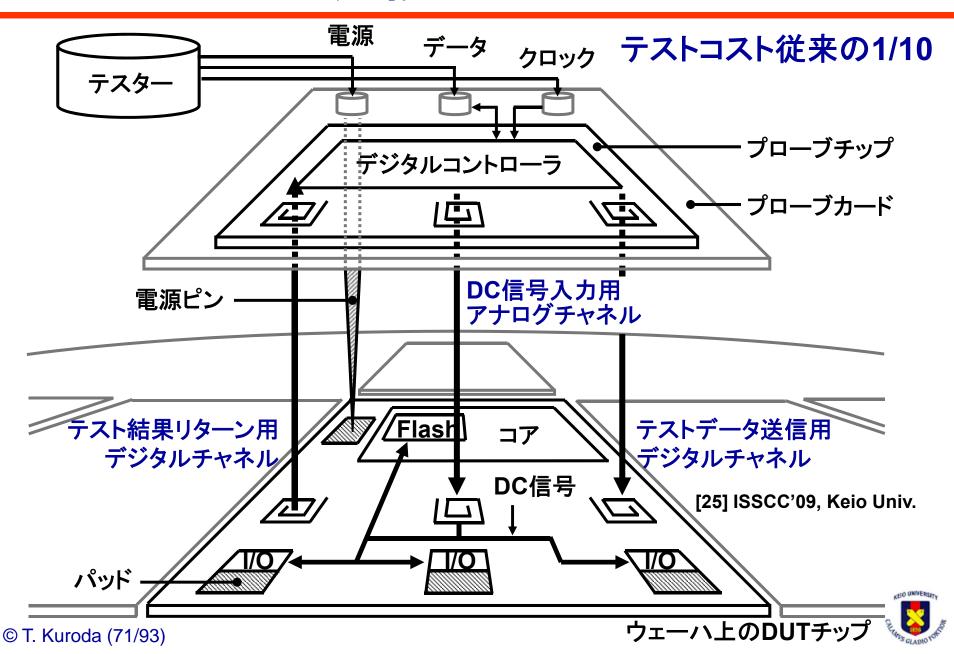

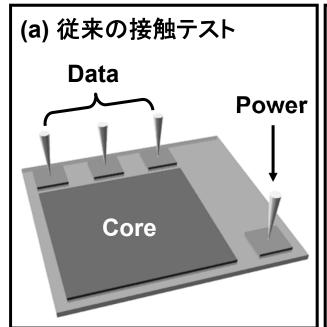

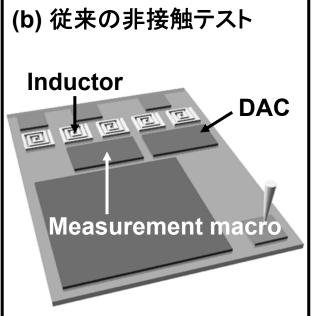

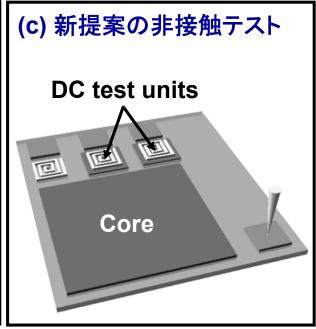

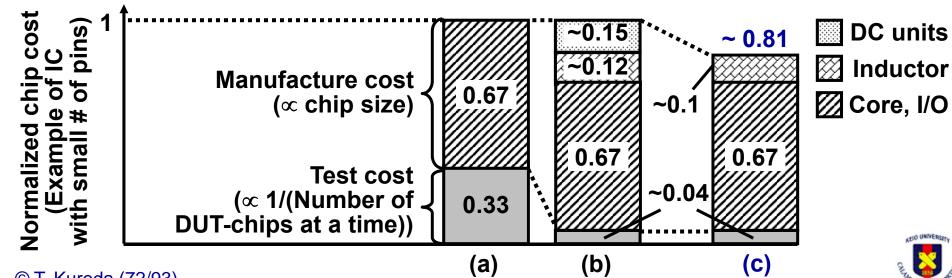

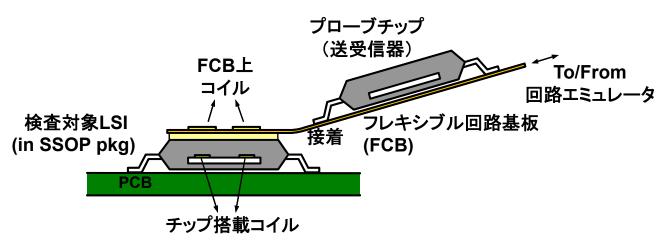

### 非接触テスト

### テストコスト削減効果

© T. Kuroda (72/93)

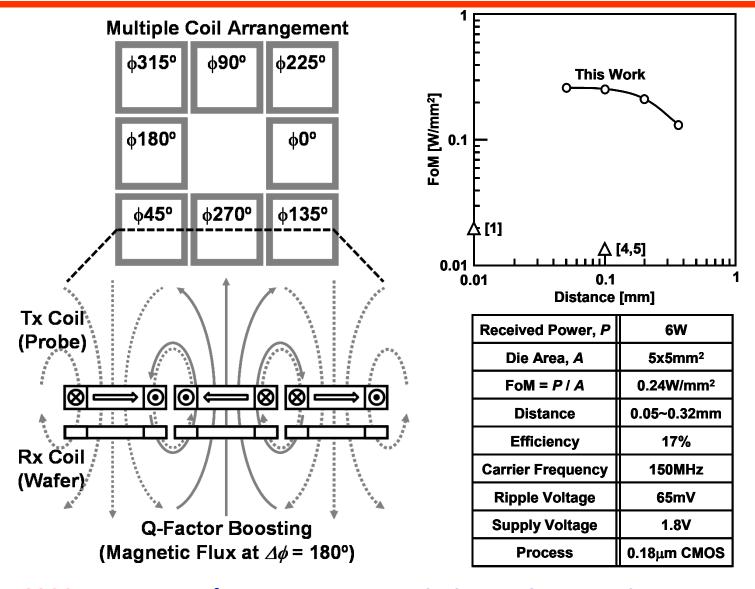

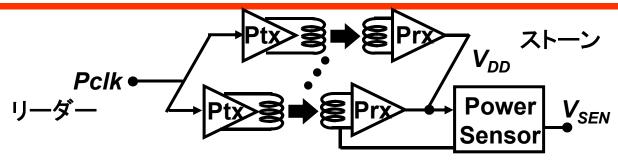

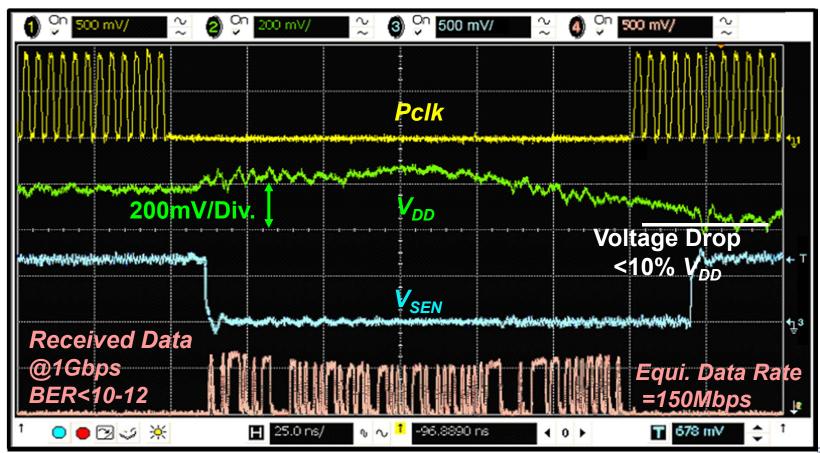

### 6W/5mmウェハー無線給電

ISSCC2011: 6W/25mm<sup>2</sup> Inductive Power Transfer for Non-Contact Wafer-Level Testing

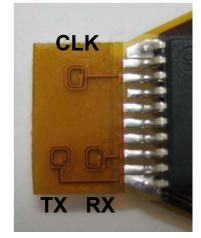

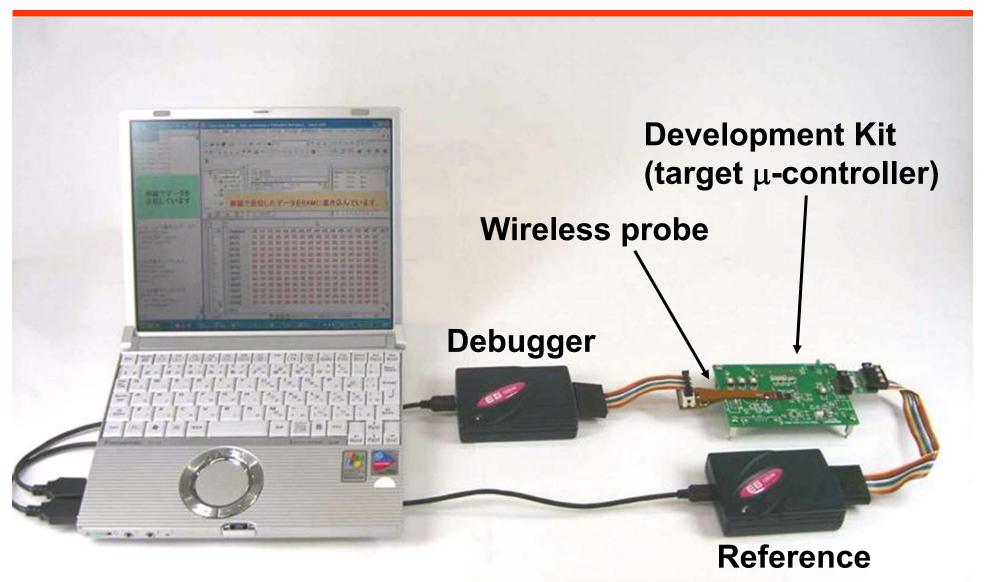

## デバッグ用バスプローブ

[10] ISSCC'07, Keio Univ.

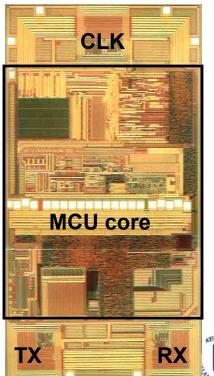

# システム検証

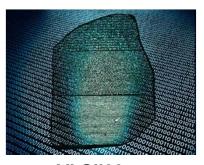

## デジタルロゼッタストーン

#### 実測波形

#### マイグレーション

■ The Digital Dilemma:

AMPAS: Academy of Motion Pictures Arts and Sciences

There is a dark side to storing information digitally.

Source: The Digital Dilemma

- 記憶装置はいずれ故障する。

- ハードディスク: 寿命30年、マイグレーション5~10年毎。回転部の故障が多い。

- デジタルテープ: 寿命5年、民生市場からやがてなくなる。

- -光ディスク (CD, DVD): 寿命15年。ホログラムは寿命50年、マイグレーション20年。

- ■マイグレーションのための費用は高い。

#### フィルム保存コスト

#### アナログ保存(今日)

#### デジタル保存(将来)

- ■4Kシネマのデータ量: 8.4 TB (53 MB/フレーム\*24 フレーム/秒\*120分\*60秒/映画)

- ■デジタルテープの保存費: \$500/TB/年

- ■映画1本のマスター保存費: \$4,171/年

- ■コピー3部保存費: \$12,514/年

- ■デジタル製作過程で作られた全ての断片的記録も保存すると、保存費は年間\$200,000以上になる。

To store a digital master record of a movie costs about \$12,514 a year, versus the \$1,059 it costs to keep a conventional film master.

Much worse, to keep the enormous swarm of data produced when a picture is "born digital" — that is, produced using all-electronic processes, rather than relying wholly or partially on film — pushes the cost of preservation to \$208,569 a year, vastly higher than the \$486 it costs to toss the equivalent camera negatives, audio recordings, on-set photographs and annotated scripts of an all-film production into the cold-storage vault. (NY Times)

**Source: The Digital Dilemma**

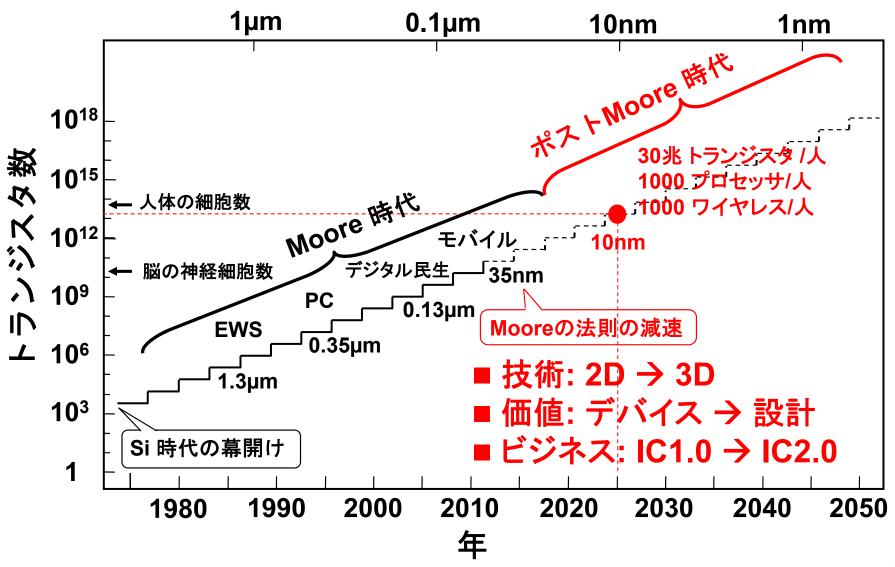

### ポスト Moore時代

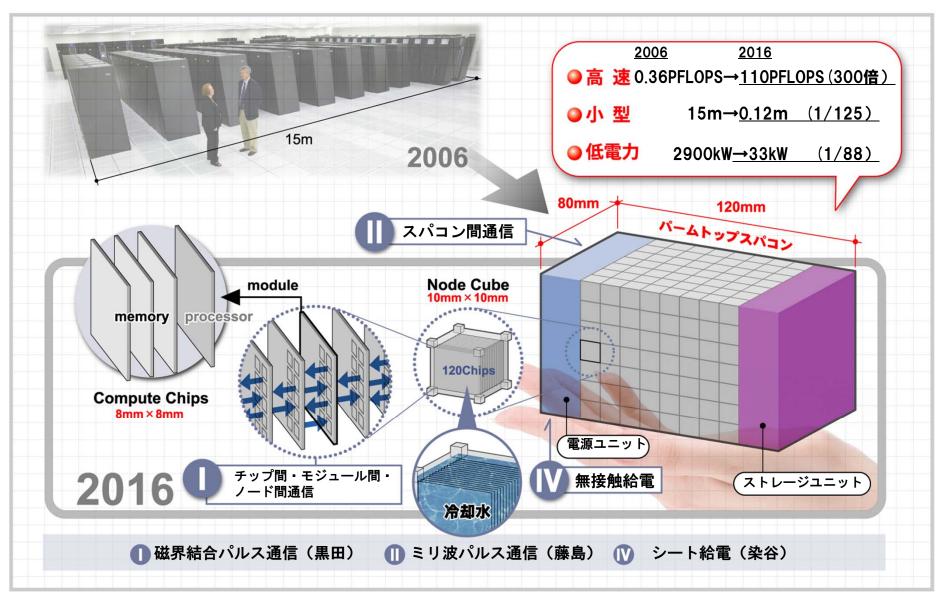

## パームトップスパコンの実現

#### 内容

- 1. 磁界結合によるチップ間通信 ThruChip Interface (TCI)

- 2. TCIの応用

- 3. 電磁界結合によるボード間通信 Coupled Transmission Line (CTL)

チップレベル 3D IC μm, 5Tbps, TCI

ボードレベル 非接触コネクタ mm, 50Gbps, CTL

#### 携帯電話やメモリカードの新インタフェース

携帯電話をかざすと、映像、音楽、写真を高速にダウン/アップロードできる。

コイル100個(3cmx3cm)

HD-DVD映像(15GB) ダウンロード 1.2秒

DVD映像(4.7GB) ダウンロード 0.4秒

音楽CD(700MB) ダウンロード 0.06秒

写真メモリカード(128MB) アップロード 0.01秒

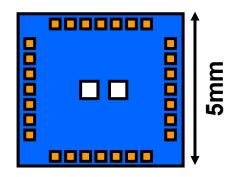

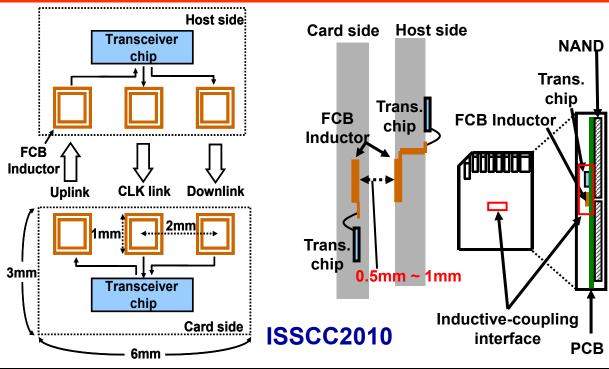

## 非接触メモリカード

| 方式   | This work       | メモリカード<br>(従来)   | mm波             | TransferJet       |

|------|-----------------|------------------|-----------------|-------------------|

| 通信距離 | 0.5mm ~<br>1mm  |                  | <1m             | <3cm              |

| 転送速度 | 2.5Gb/s/ch      | 800Mb/s          | 4Gb/s           | 300Mb/s           |

| 電力   | 6pJ/b<br>(15mW) | 78pJ/b<br>(62mW) | 77pJ<br>(308mW) | 2000pJ<br>(600mW) |

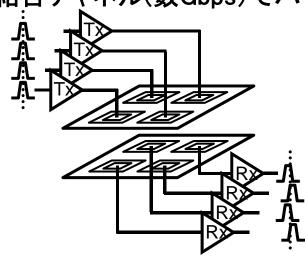

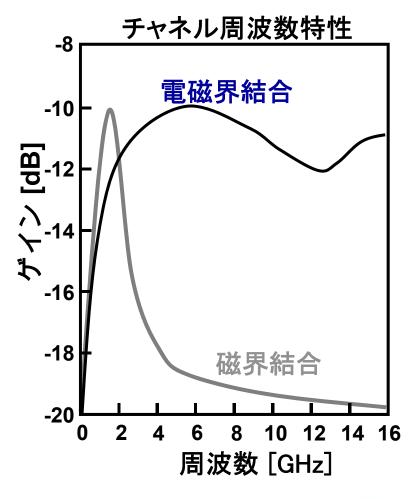

### 磁界結合から電磁界結合へ

磁界結合チャネル(数Gbps)でパラレル通信

電磁界結合チャネル(数10Gbps)でシリアル通信

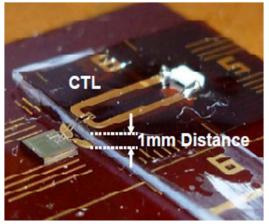

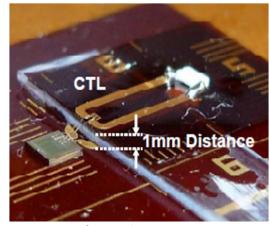

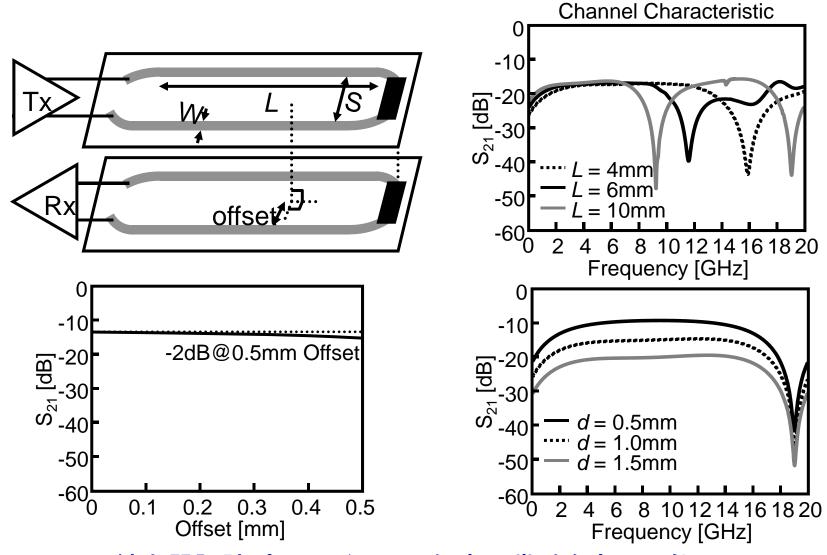

#### 伝送線路結合器

結合器設計パラメータにより任意の帯域を実現可能 通信距離、合わせずれの変動による帯域変動は非常に小さい

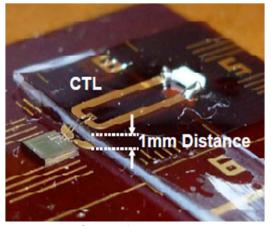

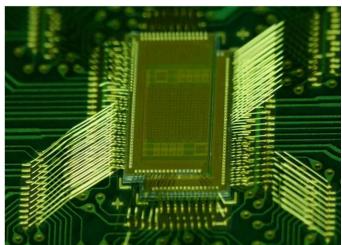

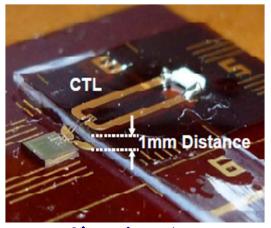

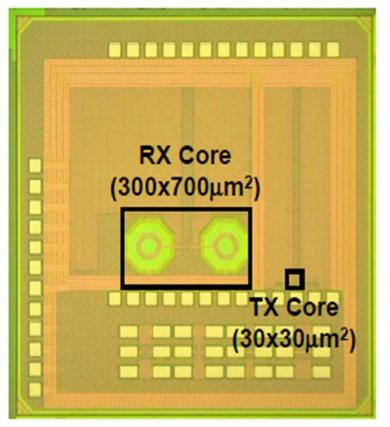

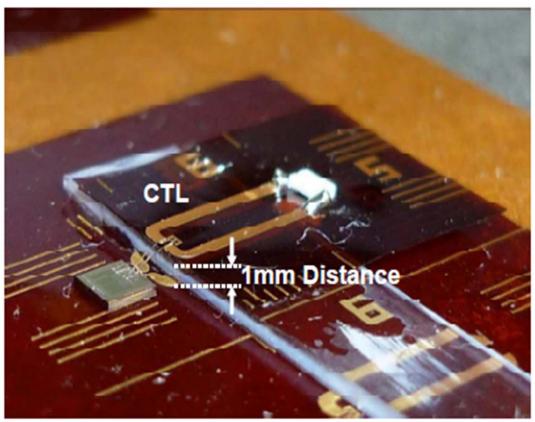

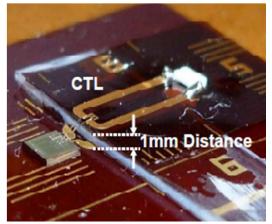

## 伝送線路型結合器と送受信チップ

90nm CMOS Interface Chip

**Evaluation Board**

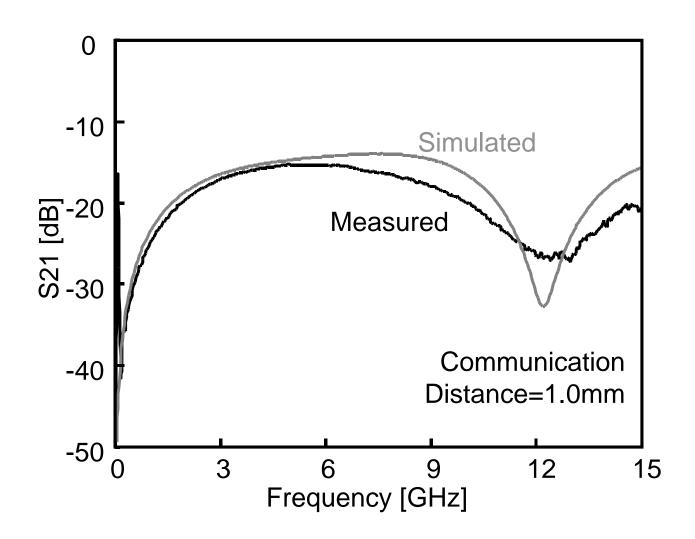

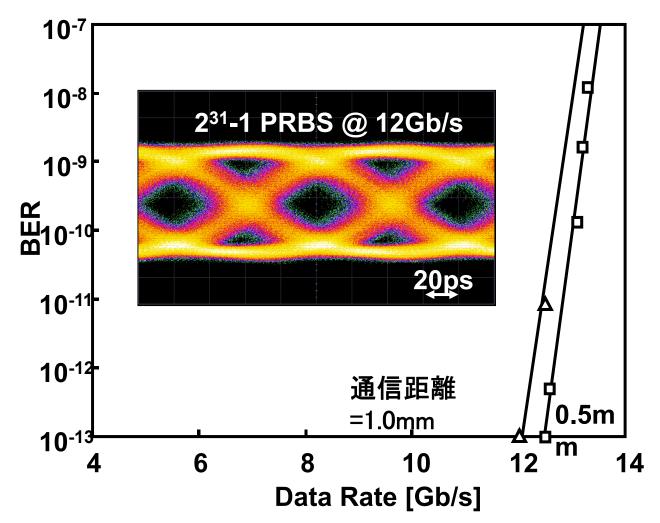

# 通信路特性

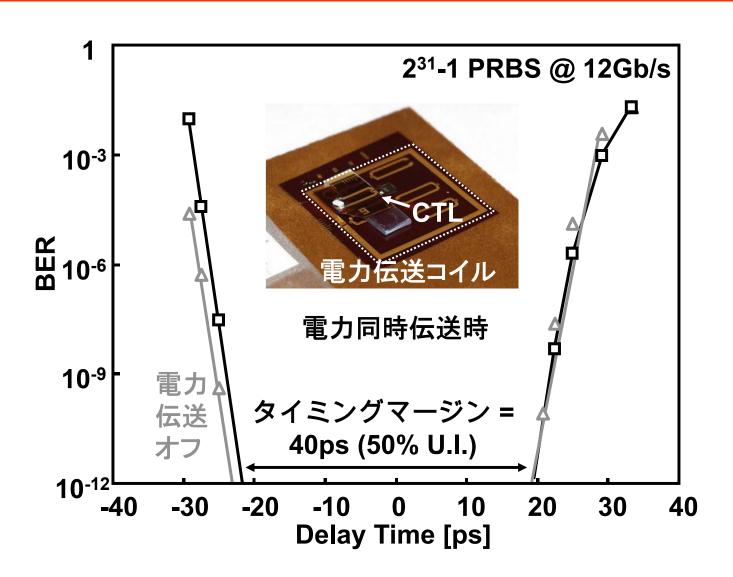

# 通信実験

12Gbpsのデータレートを達成 さらなる高速化により最終的に25Gbps/ch.を実現予定(2ch.で50Gbps)

#### 無線給電からの影響小

#### まとめ(1):磁界結合通信

- 1) TSVよりも(チップ当たり20円以上)低コスト。

- 2)標準CMOS技術とデジタルCMOS回路で実現できる。

- 3)性能はTSVと比べて引けを取らない。 転送速度:11Gb/s/ch、消費電力:0.14pJ/b、 面積:ほぼゼロ(コイルは隠せる)、信頼性:BER<10<sup>-14</sup>。

- 4) 近接場無線通信を利用。チャネルを高密度に面配列しても混信しない。

- 5)ESD保護回路が不要。電力、遅延、面積を低減できる。

- 6)ノイズ耐性が高く、チップの位置ずれにも強い。

- 7)AC結合なので、多電源・可変電源下で使いやすい。

- 8)チップの厚さを薄くすることで性能コスト比を指数関数的に改善できる。 (磁界変化一定のスケーリング則)

- 9) 磁界結合通信は実用できる。 商用レベルのプロセッサとメモリの高速通信をシステムレベルで確認。

- 10)メモリ積層、プロセッサ積層に応用できる。 SSDのパッケージ数を1/8に低減できる。

#### まとめ(2):電磁界結合通信

- 1) 電磁界結合を用いた伝送線路結合器を開発。

- 2)1mmの距離で12Gb/sを達成。

- 3)携帯電話やメモリカードの新しいインタフェースとして利用できる。

- 4)ボードレベルの非接触データ通信に応用展開できる。

チップレベル 3D IC μm, 5Tbps, TCI

ボードレベル 非接触コネクタ mm, 50Gbps, CTL

### 参考文献

- [1] D. Mizoguchi, et al., "A 1.2Gb/s/pin Wireless Superconnect Based on Inductive Inter-chip Signaling (IIS)," ISSCC, pp.142-143, Feb. 2004.

- [2] N. Miura, et al., "Analysis and Design of Inductive Coupling and Transceiver Circuit for Inductive Inter-Chip Wireless Superconnect," Symposium on VLSI Circuits, pp. 246-249, Jun. 2004.

- [3] N. Miura, et al., "Cross Talk Countermeasures in Inductive Inter-Chip Wireless Superconnect," CICC, pp.99-102, Oct. 2004.

- [4] N. Miura, et al., "A 195Gb/s 1.2W 3D-Stacked Inductive Inter-Chip Wireless Superconnect with Transmit Power Control Scheme," ISSCC, pp.264-265, Feb. 2005.

- [5] N. Miura, et al., "A 1Tb/s 3W Inductive-Coupling Transceiver for Inter-Chip Clock and Data Link," ISSCC, pp.424-425, Feb. 2006.

- [6] M. Inoue, et al., "Daisy Chain for Power Reduction in Inductive-Coupling CMOS Link," Symposium on VLSI Circuits, pp.80-81, Jun. 2006.

- [7] T. Kuroda, et al., "Perspective of Low-Power and High-Speed Wireless Inter-Chip Communications for SiP Integration," ESSCIRC, pp.3-6, Sep. 2006.

- [8] D. Mizoguchi, et al., "Constant Magnetic Field Scaling in Inductive-Coupling Data Link," SSDM, pp. 606-607, Sep. 2006.

- [9] N. Miura, et al., "A 0.14pJ/b Inductive-Coupling Inter-Chip Data Transceiver with Digitally-Controlled Precise Pulse Shaping," ISSCC, pp.264-265, Feb. 2007.

- [10] H. Ishikuro, et al., "An Attachable Wireless Chip-Access Interface for Arbitrary Data Rate Using Pulse-Based Inductive-Coupling through LSI Package," ISSCC. pp.266-267. Feb. 2007.

- [11] H. Ishikuro, et al., "Wideband Inductive-coupling Interface for High-performance Portable System," CICC, pp.13-20, Sep. 2007.

- [12] Y. Yoshida, et al., "A 2Gb/s bi-directional inter-chip data transceiver with differential inductors for high density inductive channel array," A-SSCC, pp.127-130. Nov. 2007.

- [13] K. Niitsu, et al., "Interference from Power/Signal Lines and to SRAM Circuits in 65nm CMOS Inductive-Coupling Link," A-SSCC, pp.131-134, Nov. 2007.

- [14] N. Miura, et al., "An 11Gb/s Inductive-Coupling Link with Burst Transmission," ISSCC, pp.298-299, Feb. 2008.

- [15] K. Niitsu, et al., "Misalignment Tolerance in Inductive-Coupling Inter-Chip Link for 3D System Integration," SSDM, pp.86-87, Sep. 2008.

- [16] K. Niitsu, et al., "A 65fJ/b Inductive-Coupling Inter-Chip Transceiver Using Charge Recycling Technique for Power-Aware 3D System Integration," A-SSCC, pp.97-100, Nov. 2008.

- [17] S. Kawai, et al., "A Real-Time On-Chip Bus Trace System Using Quasi-Synchronous Inductive Coupling Transceiver," A-SSCC, pp.113-116, Nov. 2008.

- [18] Y. Sugimori, et al., "A 2Gb/s 15pJ/b/chip Inductive-Coupling Programmable Bus for NAND Flash Memory Stacking," ISSCC, pp.244-245, Feb. 2009.

- [19] Y. Yoshida, et al., "Wireless DC Voltage Transmission Using Inductive-Coupling Channel for Highly-Parallel Wafer-Level Testing," ISSCC, pp.470-472, Feb. 2009.

- [20] K. Niitsu, et al., "An Inductive-Coupling Link for 3D Integration of a 90nm CMOS Processor and a 65nm CMOS SRAM," ISSCC, pp.480-481, Feb. 2009.

- [21] K. Osada, et al., "3D System Integration of Processor and Multi-Stacked SRAMs by Using Inductive-Coupling Links," Symposium on VLSI Circuits, pp.256-257, Jun. 2009.

- [22] Y. Kohama, et al., "A Scalable 3D Processor by Homogeneous Chip Stacking with Inductive-Coupling Link," Symposium on VLSI Circuits, pp.94-95, Jun. 2009.

- [23] S. Kawai, et al., "A 4.7Gb/s Inductive Coupling Interposer with Dual Mode Modem," Symposium on VLSI Circuits, pp.92-93, Jun. 2009.

- [24] Y. Yuxiang, et al., "Digital Rosetta Stone: A Sealed Permanent Memory with Inductive-Coupling Power and Data Link," Symposium on VLSI Circuits, pp.26-27. Jun. 2009.

- [25] M. Saito, et al., "47% Power Reduction and 91% Area Reduction in Inductive-Coupling Programmable Bus for NAND Flash Memory Stacking," CICC, pp. 449-452, Sep. 2009.

- [26] K. Kasuga, et al., "Electromagnetic Interference and Susceptibility in Inductive-Coupling Link," SSDM, pp. 62-63, Oct. 2006.

- [27] M. Saito, et al., "An Extended XY Coil for Noise Reduction in Inductive-Coupling Link," A-SSCC, Nov. 2008.

- [28] K. Kasuga, et al., "A Wafer Test Method of Inductive-Coupling Link," A-SSCC, Nov. 2008.

- [29] N. Miura, et al., "An 8Tb/s 1pJ/b 0.8mm2/Tb/s QDR Inductive-Coupling Interface Between 65nm CMOS GPU and 100nm DRAM," ISSCC, Feb. 2010.

- [30] S. Kawai, et al., "A 2.5Gb/s/ch 4PAM-AGPC Inductive-Coupling Transceiver for Non-Contact Memory Card," ISSCC, Feb. 2010.

- [31] M. Saito, et al., "A 2Gb/s 1.8pJ/b/chip Inductive-Coupling Through-Chip Bus for 128-Die NAND Flash Memory Stacking," ISSCC, Feb. 2010.